تعتمد أوروبا بشكل كبير على التكنولوجيا المصممة والمنتجة في الولايات المتحدة والصين. هذا هو السبب في أن بعض الأشياء كانت تتحرك منذ بضع سنوات على مستوى الاتحاد الأوروبي بحيث يتوقف هذا عن أن يكون هو الحال ، و تتمتع بالاستقلالية ، خاصة في مجال الحوسبة. ظهرت مشاريع مثل EPI و eProcessor وشركات مثل SiPearl ، بالإضافة إلى البنية التحتية GAIA-X من هذه الحركات.

نظرًا لأن معظم ISA أو البنى مملوكة ومملوكة خارج أوروبا ، المصدر المفتوح لقد كان مفتاح نجاح هذه المشاريع. ال عيسى RISC-V لقد جلبت الأمل ، مما سمح لهذه المعالجات والمسرعات بالبناء عليها دون أي قيود أو قيود بسبب الحروب الجيوسياسية والجيواستراتيجية.

ولادة EPI (مبادرة المعالج الأوروبي)

كان من أولى ردود الفعل في أوروبا ، بعد مؤتمر EDA (وكالة الدفاع الأوروبية) حيث تم الكشف عن مشاكل الاعتماد التكنولوجي والصناعي للدول الأعضاء ، بدء مبادرة مشتركة تسمى EPI (مبادرة المعالج الأوروبي). هدفها هو الجمع بين كونسورتيوم لتنفيذ الآليات اللازمة للحصول على معالجات مصممة في أوروبا.

هذه الرقائق ، من حيث المبدأ ، لن تكون للاستخدام الخاص ، ولكنها ستركز عليها قطاع HPC، وهي الحوسبة الفائقة. تعتبر هذه الآلات عالية الأداء بالغة الأهمية ، ونتيجة لهذا المشروع ، سيتم ترقية مراكز بيانات الاتحاد الأوروبي إلى Exascale اعتبارًا من عام 2023. وسيكون لها أيضًا تطبيقات في قطاعات أخرى مثل صناعات السيارات والطيران.

لجعل هذا ممكنا ، على أساس RISC-V بالنسبة للمسرعات ، بينما تعتمد GPPs أو معالجات الأغراض العامة على نوى IP ARM Cortex Neoverse ، لأنها ستسمح لهم بتسريع عملية التصميم وعدم البدء من الصفر.

EPI لديها أيضا 26 شريكًا من 10 دول أوروبية مختلفة ، بما في ذلك إسبانيا. أحد الركائز الأساسية للمشروع هو مركز برشلونة الوطني للحوسبة الفائقة (BCN). انضم إلى إسبانيا شركاء مثل Chalmers Tekniska Hoegskola AB من السويد ، Infineon Technologies من ألمانيا ، CEA من فرنسا ، STMicroelectronics في هولندا ، جامعة بولونيا في إيطاليا ، المعهد التقني العالي في لشبونة في البرتغال ، FORTH في اليونان ، أو ETH معمل زيورخ من سويسرا.

تم إنشاء SiPearl ، الشركة الخاصة ، لتزويد المشروع بالقدرة على العمل

من أجل العمل ، تم إنشاء شركة خاصة ستكون مسؤولة عن إدارة التقنيات الناتجة عن مشروع EPI هذا. اسمه هو نعم ومقرها في فرنسا. بالإضافة إلى ذلك ، فقد افتتحوا شركة فرعية في ألمانيا وأخرى في إسبانيا ، وتحديداً في برشلونة ، من أجل أن يكونوا قريبين من شركائهم في شركة BSC.

بدأت هذه الشركة الناشئة بميزانية عامة تبلغ 80 millones دي يورو، والتي لا تكفي لتغطية جميع النفقات التي ينطوي عليها مشروع بهذا العمق. لذلك ، ستكون SiPearl مسؤولة أيضًا عن جمع أكثر من 100 مليون يورو من القطاع الخاص ، معظمها من الأسهم.

المؤسس المشارك والرئيس التنفيذي ، فيليب نوتن، يقوم بعمل رائع في توظيف بعض المصممين الذين تم جلبهم من وادي السيليكون ، بالإضافة إلى الموظفين المناسبين ذوي الخبرة لمنح المشروع جميع الضمانات. إنهم يبحثون أيضًا عن شركاء تقنيين ، مثل Graphcore ، وهي شركة بريطانية رائدة من حيث تسريع الرقائق ذات الذكاء الاصطناعي والتي تعتبر مهمة جدًا في HPC.

BSC شريك رئيسي: من شريحة Lagarto إلى Drac

El BSC (مركز برشلونة للحوسبة الفائقة) إنه جزء أساسي من هذا المشروع. إنهم لا يساهمون فقط في تصميم وتطوير هذه المعالجات ، ولكن Marenostrum 5 سيبدأ بالفعل في اختبار ثمار هذا المشروع ...

اجارتو

تمت دبلجة أول معالج دقيق إسباني يعتمد على مجموعة تعليمات RISC-V اجارتو، وهي الخطوة الأولى للوصول إلى الاستقلال التكنولوجي. ومع ذلك ، يوجد خلف هذا المشروع جهد كبير وعمل منسق من قبل BSC للمركز الوطني للحوسبة الفائقة في إسبانيا ، بالإضافة إلى تعاون CSIC و UPC.

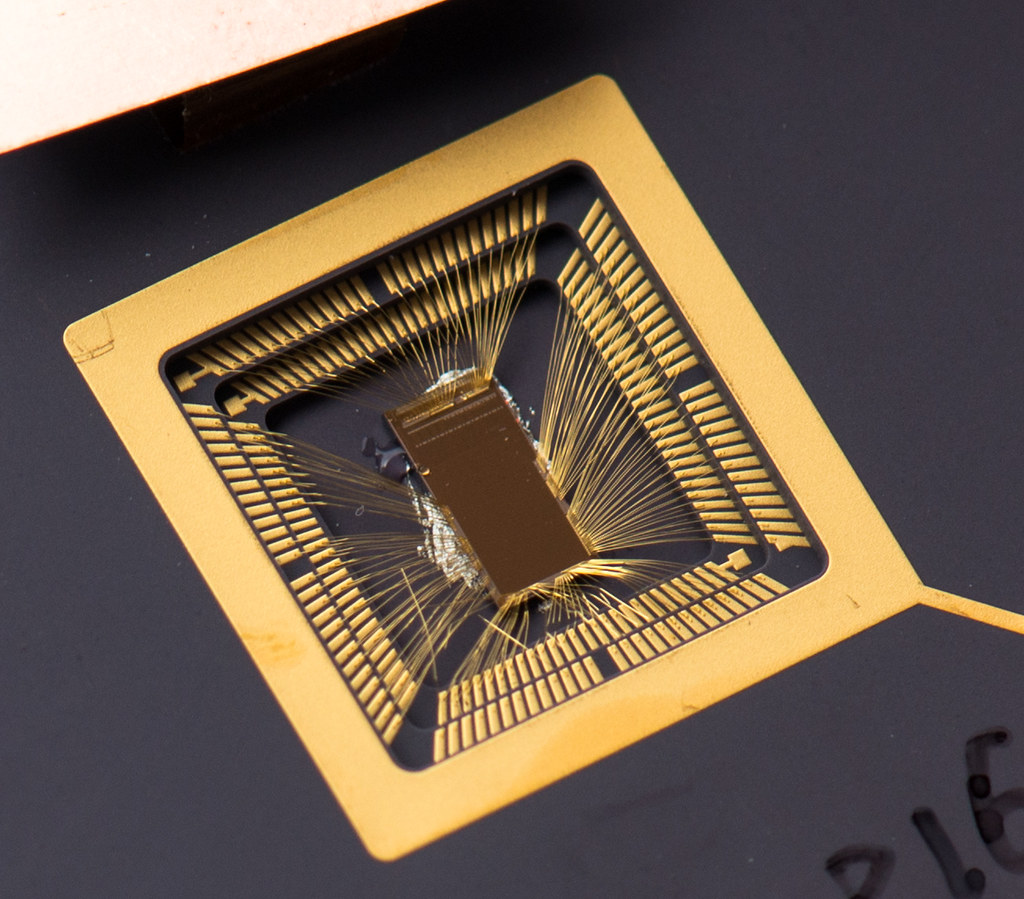

هذا التصميم بسيط للغاية وهدفك هو إجراء الاختبارات الأولى. تم تصنيعه باستخدام عقدة 65 نانومتر في TSMC، وهو ما يكفي للبساطة النسبية لهذا النموذج الأولي المبكر الذي تم اختباره في بعض المعايير لمعرفة ما هو قادر عليه ، وكانت النتائج إيجابية للغاية. حتى أفضل مما كان متوقعا ...

في مايو 2019 ، سيتم إرسال التصميم النهائي لهذه الشريحة إلى منصة EUROPRACTICE من المفوضية الأوروبية ، وبعد ذلك ستصل حوالي 100 نسخة من لاغارتو إلى برشلونة لبدء الاختبارات ولتكون بمثابة الأساس لمسرّع HPC الذي يعتمد أيضًا على هذا المعيار.

دراك

كانت الخطوة التالية دراك (تصميم مسرعات RISC-V-bsed للجيل القادم من أجهزة الكمبيوتر). شريحة مصممة لتطبيقات الأمان ، مثل تشفير الأجهزة ، بالإضافة إلى التطبيقات العلمية مثل تحليل الجينوم أو تسريع المحاكاة أو قطاع المركبات المستقلة.

بالطبع ، يقود DRAC أيضًا BSC ويستند إلى بنية مفتوح المصدر RISC-V. من المتوقع أن يستمر هذا المشروع حوالي 3 سنوات ، وسيشارك فيه ما يصل إلى 40 باحثًا وسيتم تنسيقه بواسطة ميكيل موريتو ، الباحث من برنامج Ramón y Cajal في UPC. بالإضافة إلى ذلك ، كان التمويل حوالي 4 ملايين يورو ، نصفها من أموال ERDF والنصف الآخر من شركاء هذا المشروع.

لقد بدأ هذا بالفعل يؤتي ثماره. DVINO (ناقل DRAC بالترتيب) وهي شريحة مستمدة من هذا المشروع ومن الجيل الأول. كما يوحي اسمه ، فهو IC جيد الترتيب يتضمن نواة Lagarto إلى جانب معالج Hydra vector المصمم للحوسبة الموزعة.

La الجيل الثاني تحسين أداء الرقاقة بنسبة 15٪ وإضافة برامج تشغيل جديدة وزيادة المساحة إلى 8.6 ملم مربع.

المعالج الإلكتروني

المعالج الإلكتروني هي خطوة جديدة للأمام ، معالج بإصدارات مخططة للحوسبة الفائقة والخوادم ، بالإضافة إلى أنظمة مساعدة السائق المتقدمة للمركبات (على سبيل المثال: ADAS) ، وإنترنت الأشياء ، والأجهزة المحمولة ، إلخ.

مرة أخرى BSC هو الشخص الذي يشارك في هذا المشروع. إنه أول نظام بيئي أوروبي مكدس مفتوح المصدر ، وستكون ركائزه المركزية هي وحدة المعالجة المركزية القائمة على RISC-V ومع kernel مع تنفيذ خارج الترتيب. سيساهم مركز برشلونة بخبرته في تصميم نوى IP في HDL والمحاكاة والأدوات اللازمة.

جنبا إلى جنب مع BSC ، أخرى أعضاء مهمين على المستوى الأوروبي، مثل جامعة تشالمرز للتكنولوجيا ، ومؤسسة هيلاس للأبحاث والتكنولوجيا ، وجامعة ديجلي ستودي دي روما لا سابينزا ، وكورتوس ، وكريستمان لتقنية المعلومات ، وجامعة بيليفيلد ، وإكستول ، وتاليس ، وإكسابسيس ، فضلاً عن دعم EuroHPC JU.

سيتم تطوير تقنيات الأجهزة والبرامج والبدء فيها الاختبار على FPGAs ثم يعطي الصلاة ل ASICs. ستكون الخطوة الأولى هي تصميم نواة RISC-V عالية الأداء وعالية الكفاءة. ستكون أحادية النواة وثنائية النواة مع ارتباط متماسك خارج الشريحة ، على الرغم من أنها ستبدأ لاحقًا بتصميمات أكثر تعقيدًا وقوة. سيتم أيضًا تصميم مسرع المتجه المستند إلى RISC-V واستكشاف أعباء عمل الحوسبة الفائقة التقليدية مثل المعلوماتية الحيوية ، والذكاء الاصطناعي ، و HPDA ، وما إلى ذلك.

سيكون المعالج الإلكتروني أيضًا متعددة الاستخدامات ومرنة للغاية في وقت توسيعه ، لتتمكن من إضافة المزيد من الأجهزة على الرقاقة.

الخطوة التالية: التصنيع

سيكون تصميم هذه الرقائق أوروبيًا ، ولن يكون التصنيع. SiPearl هي صناعة خالية من المواد الخام ، وبالنظر إلى تراكم عقد تصنيع المسبك في البلدان الأعضاء ، فقد تم التصميم بتكليف من TSMC، والتي ستصنعها بتقنية 7 نانومتر وباستخدام تقنية تغليف ثلاثية الأبعاد جديدة تسمى CoWoS (رقاقة على رقاقة على الركيزة).

ومع ذلك ، فإن الفكرة ليست الاعتماد على المصانع الأجنبية لذلك ، كما فعل الاتحاد الأوروبي أيضًا حشد جزء كبير من المال لتمويل تحديث صناعة أشباه الموصلات في القارة القديمة. على وجه التحديد ، ستخصص 145.000 مليون يورو ، بهدف الوصول إلى عقدة بتقنية تصنيع 2 نانومتر على المدى القصير.

هذا يستغرق وقتًا ويهدف إلى الوصول إليه 2-3 سنوات شوهد. بالإضافة إلى ذلك ، يبدو أن TSMC تتعاون لجعل هذا ممكنًا ، وكذلك ASML الأوروبية ، وهي الشركة الرائدة في تصنيع آلات الطباعة الحجرية الضوئية المتقدمة لصناعة أشباه الموصلات ، ومقرها هولندا ...

أوضحت نادية كالفينو نفسها ، نائبة الرئيس للشؤون الاقتصادية والتحول الرقمي ، الأمر على النحو التالي: «يجري العمل على الصعيدين الوطني والدولي ل تعرف على الشركات الإسبانية والأوروبية التي يمكنها تصنيعها«، في إشارة إلى هذه الرقائق. وعلى نفس المنوال كان خطاب تييري بريتون في المفوضية الأوروبية. وهي أن الأموال المخصصة للقطاع ستأتي إلى حد كبير من المساعدة التي يقدمها الاتحاد الأوروبي للتحول الرقمي وللتعافي بعد الوباء.