Europa té una forta dependència de la tecnologia dissenyada i produïda als Estats Units i la Xina. Per això, des de fa uns anys, s'estan movent algunes coses a nivell de la UE perquè això deixi de ser així, i poder tenir independència, especialment en la computació. D'aquests moviments han sorgit projectes com EPI, eProcessor, empreses com SiPearl, així com la infraestructura GAIA-X.

Atès que la majoria de les ISAs o arquitectures són propietàries i estan en mans fora d'Europa, el codi obert ha estat clau perquè aquests projectes puguin tirar endavant. la ISA RISC-V ha portat l'esperança, permetent que aquests processadors i acceleradors es basin en ella sense cap tipus de restricció ni limitació per guerres geopolítiques i geoestratègiques.

Neix EPI (European Processor Initiative)

Una de les primeres reaccions d'Europa, després de la conferència d'EDA (European Defense Agency) on es van exposar els problemes per la dependència tecnològica i industrial dels països membres, va ser iniciar una iniciativa conjunta anomenada EPI (European Processor Initiative). El seu objectiu és agrupar un consorci per posar en marxa els mecanismes necessaris per disposar de processadors dissenyats a Europa.

Aquests xips, en principi, no seran per a ús particular, sinó que se centraran en el sector HPC, És a dir, la supercomputació. Aquestes màquines d'alt rendiment són especialment crítiques, i amb el fruit d'aquest projecte s'impulsarà als centres de dades de la UE cap a la Exaescala a partir de 2023. També tindran aplicació en altres sectors com la indústria de l'automòbil i l'aeroespacial.

Per fer això possible, s'han basat en RISC-V per als acceleradors, mentre que els GPP o processador de propòsit general, es basaran en nuclis IP ARM Cortex Neoverse, atès que els permetran accelerar el procés de disseny i no començar des de zero.

EPI compta també amb 26 socis de 10 països europeus diferents, entre ells Espanya. Un dels pilars centrals de el projecte és el Centre Nacional de Supercomputació de Barcelona (BCN). A Espanya s'uneixen socis com Chalmers Tekniska Hoegskola AB de Suècia, Infineon Technologies d'Alemanya, CEA de França, STMicroelectronics a Holanda, la Università di Bologna d'Itàlia, l'Institut Superior Tècnic de Lisboa a Portugal, FORTH de Grècia, o el laboratori ETH Zürich de Suïssa.

Es crea SiPearl, l'empresa privada per dotar el projecte de capacitat d'operar

Per poder operar, s'ha creat una empresa privada que s'encarregarà de gestionar les tecnologies resultants d'aquest projecte EPI. El seu nom és SiPearl i el seu quarter general es troba a França. A més, han obert una filial a Alemanya i una altra a Espanya, concretament a Barcelona, per així estar prop dels seus socis de l'BSC.

Aquesta startup partia amb un pressupost públic de 80 milions d'euros, Que no són suficients per cobrir totes les despeses que un projecte de tal envergadura implica. Per tant, SiPearl també s'encarregarà de recaptar més de 100 milions d'euros privats, principalment d'accions.

El seu cofundador i CEO, Philippe Notton, Està fent una tasca fantàstica reclutant a alguns dissenyadors portats des Silicon Valley, així com el personal adequat amb l'experiència per dotar el projecte de totes les garanties. També estan buscant socis a nivell tecnològic, com és el cas de Graphcore, una companyia britànica líder pel que fa a acceleració xips amb intel·ligència artificial que resulten tan importants en el HPC.

BSC un soci clau: De el xip Lagarto fins Drac

El BSC (Barcelona Supercomputing Center) és una peça clau d'aquest projecte. No només estan contribuint a el disseny i desenvolupament d'aquests processadors, sinó que el Marenostrum maig començarà ja a provar els fruits d'aquest projecte ...

llangardaix

El primer microprocessador espanyol basat en el repertori d'instruccions RISC-V s'ha batejat com llangardaix, I és el primer pas per arribar a la independència tecnològica. No obstant això, després d'aquest projecte hi ha un gran esforç i treball coordinat pel BSC de el Centre Nacional de Supercomputació d'Espanya, així com la col·laboració de l'CSIC, i la UPC.

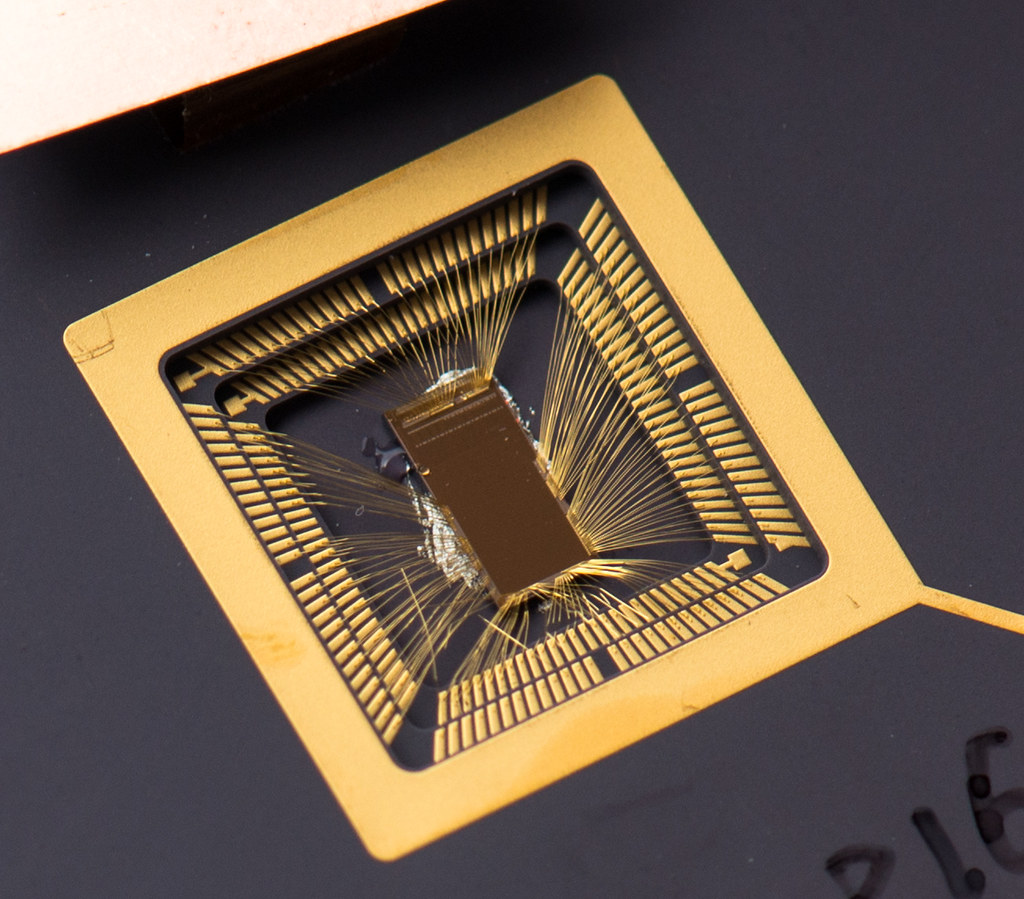

Aquest disseny és molt senzill, i el seu objectiu és realitzar les primeres proves. Es va fabricar usant un node de 65nm a TSMC, Suficient per la relativa senzillesa d'aquest prototip d'hora que va ser provat en alguns benchmarks per veure de què era capaç, i els resultats van ser força positius. Fins i tot millor del que s'esperava ...

Al maig de 2019 s'enviaria el disseny final d'aquest xip a la plataforma EUROPRACTICE de la CE, i després d'això arribarien uns 100 exemplars de Lagarto a Barcelona per començar amb les proves i que serveixi com a base per a l'accelerador per al HPC que s'està basant també en aquesta ISA.

DRAC

El següent pas va ser DRAC (Designing RISC-V-bsed Accelerators for the next generation Computers). Un xip dissenyat per a aplicacions de seguretat, com el xifrat per maquinari, així com també aplicacions científiques com l'anàlisi de l'genoma, acceleració de simulacions, o el sector dels vehicles autònoms.

Per descomptat, DRAC també està liderat pel BSC i es basa en l'arquitectura de codi obert RISC-V. Aquest projecte té previst durar uns 3 anys, en què participaran fins a 40 investigadors i serà coordinat per Miquel Moretó, un investigador de el programa Ramón i Cajal de la UPC. A més, el finançament ha estat d'uns 4 milions d'euros, la meitat procedents de fons FEDER i l'altra meitat dels socis d'aquest projecte.

Això ja ha començat a donar els seus fruits. DVI (DRAC Vector IN-Order) és un xip derivat d'aquest projecte i de primera generació. Com el seu propi nom deixa intuir, es tracta d'un CI en ordre que inclou un nucli Llangardaix juntament amb un processador vectorial Hydra pensat per a la computació distribuïda.

La segona generació millorar el rendiment de l'xip en un 15% i afegeix nous controladors i s'ha incrementat l'àrea fins 8.6 mil·límetres quadrats.

eProcessor

eProcessor és el nou pas a el front, un processador amb versions previstes per a la supercomputació i servidors, així com sistemes avançats d'assistència a l'conductor per a vehicles (pe: ADAS), IOT, dispositius mòbils, etc.

Novament el BSC és el que està ficat en aquest projecte. Es tracta del primer ecosistema full-stack europeu de codi obert i el pilar central serà una CPU basada en RISC-V i amb un nucli amb execució fora d'ordre. El centre de Barcelona aportarà la seva experiència en el disseny de nuclis IP en HDL, emulació, i eines necessàries.

Juntament amb el BSC, s'han implicat altres membres importants a nivell europeu, Com la Universitat Tecnològica de Chalmers, la Foundation for Research and Technology Hellas, Universita degli Studi di Roma La Sapienza, Cortus, Christmann Informationstechnik, Universität Bielefeld, Extoll GmbH, Thales i Exapsys, així com el suport de EuroHPC JU.

Es desenvoluparan tecnologies de maquinari i programari que es començaran provant en FPGAs per després donar el salato als ASICs. El primer pas serà dissenyar un nucli RISC-V d'alt rendiment i alta eficiència. Serà un single-core i un dual-core amb enllaç coherent off-xip, encara que després es començaran amb dissenys més complexos i potents. També es dissenyarà l'accelerador vectorial basat en RISC-V i s'exploraran càrregues de treball tradicionals en supercomputació, com la bioinformàtica, IA, HPDA, etc.

El eProcessor serà també molt versàtil i flexible a l'hora d'escalar-, per poder anar afegint més dispositius on-xip.

El següent pas: la fabricació

El disseny d'aquests xips serà europeu, el que no serà és la fabricació. SiPearl és una fabless, i donat l'endarreriment pel que fa als nodes de fabricació de les foundries en països membres, el disseny s'ha encarregat a TSMC, Que el fabricarà en tecnologia de 7nm i usant la nova tecnologia d'empaquetat 3D anomenada CoWoS (Xip-on-Wafer-on-Substrate).

No obstant això, la idea és no dependre de factories estrangeres per això, de manera que la UE també ha mobilitzat una gran part de diners per finançar la posada a el dia de la fabricació de semiconductors en el Vell Continent. Concretament destinarà 145.000 milions d'euros, amb l'objectiu d'arribar a un node amb tecnologia de fabricació de 2nm a curt termini.

Això necessita de temps, i es pretén que arribi a 2-3 anys vista. A més, sembla que TSMC està col·laborant en que això sigui possible, i també l'europea ASML, que és el líder pel que fa a la fabricació de màquines per a la fotolitografia avançada per a la indústria dels semiconductors, i que té seu a Països Baixos ...

La pròpia Nadia Calviño, vicepresidenta d'Afers Econòmics i Transformació Digital ho ha explicat així: «S'està treballant a nivell nacional i internacional per a veure quines empreses espanyoles i europees poden fabricar-«, En referència i aquests xips. En la mateixa línia va ser el discurs de Thierry Breton a la Comissió Europea. I és que els fons destinats a el sector sortiran en gran mesura de les ajudes prestades per la UE per a la transformació digital i per a la recuperació post-pandèmia.