Europa er stærkt afhængig af teknologi designet og produceret i USA og Kina. Af den grund har der i nogle år bevæget sig nogle ting på EU-plan, så det ikke længere er tilfældet, og for at kunne har uafhængighed, især inden for databehandling. Ud af disse bevægelser er der opstået projekter som EPI, eProcessor, virksomheder som SiPearl samt GAIA-X-infrastrukturen.

Da de fleste af ISA'erne eller arkitekturerne er proprietære og i hænder uden for Europa, åben kildekode Det har været afgørende for disse projekter at komme videre. Det ISA RISC-V det har bragt håb, hvilket giver disse processorer og acceleratorer mulighed for at bygge videre på det uden nogen form for begrænsning eller begrænsning af geopolitiske og geostrategiske krige.

EPI (European Processor Initiative) er født

En af de første reaktioner i Europa, efter EDA-konferencen (European Defense Agency), hvor problemerne forårsaget af medlemslandenes teknologiske og industrielle afhængighed blev afsløret, var at igangsætte et fælles initiativ kaldet EPI (European Processor Initiative). Dens mål er at samle et konsortium for at implementere de nødvendige mekanismer for at få processorer designet i Europa.

Disse chips vil i princippet ikke være til privat brug, men vil fokusere på HPC-sektoren, altså supercomputing. Disse højtydende maskiner er særligt kritiske, og frugten af dette projekt vil drive datacentre i EU mod Exascale fra 2023. De vil også finde anvendelser i andre sektorer såsom bil- og rumfartsindustrien.

For at gøre dette muligt, har de baseret på RISC-V for acceleratorerne, mens GPP eller General Purpose Processor, vil være baseret på ARM Cortex Neoverse IP-kerner, da det vil give dem mulighed for at fremskynde designprocessen og ikke starte fra bunden.

Det har EPI også 26 partnere fra 10 forskellige europæiske lande, herunder Spanien. En af de centrale søjler i projektet er Barcelona National Supercomputing Center (BCN). Spanien får selskab af partnere som Chalmers Tekniska Hoegskola AB fra Sverige, Infineon Technologies fra Tyskland, CEA fra Frankrig, STMicroelectronics i Holland, Università di Bologna fra Italien, Instituto Superior Técnico de Lisboa i Portugal, FORTH fra Grækenland, eller ETH laboratorium, Zürich i Schweiz.

SiPearl, den private virksomhed, er oprettet for at give projektet kapacitet til at fungere

For at kunne fungere er der oprettet en privat virksomhed, som skal stå for forvaltningen af de teknologier, der er et resultat af dette EPI-projekt. Hans navn er JaPearl og dets hovedkvarter er i Frankrig. Derudover har de åbnet et datterselskab i Tyskland og et andet i Spanien, specifikt i Barcelona, for at være tæt på deres BSC-partnere.

Denne opstart startede med et offentligt budget på 80 millioner euro, som ikke er nok til at dække alle de udgifter, som et projekt af denne størrelsesorden medfører. Derfor vil SiPearl også stå for at rejse mere end 100 millioner private euro, primært fra aktier.

Dets medstifter og administrerende direktør, Philippe Notton, gør et fantastisk stykke arbejde med at rekruttere nogle designere hentet fra Silicon Valley, samt det rigtige personale med erfaringen til at give projektet alle garantierne. De leder også efter partnere på et teknologisk niveau, som det er tilfældet med Graphcore, en førende britisk virksomhed i forhold til at accelerere chips med kunstig intelligens, der er så vigtige i HPC.

BSC en nøglepartner: Fra Lagarto-chippen til Drac

El BSC (Barcelona Supercomputing Center) er en central del af dette projekt. Ikke alene bidrager de til design og udvikling af disse processorer, men Marenostrum 5 vil allerede begynde at teste frugterne af dette projekt...

firben

Den første spanske mikroprocessor baseret på RISC-V instruktionssættet er blevet døbt som firben, og det er det første skridt til at nå teknologisk uafhængighed. Men bag dette projekt ligger der en stor indsats og arbejde koordineret af BSC for det nationale supercomputingcenter i Spanien, samt samarbejdet mellem CSIC og UPC.

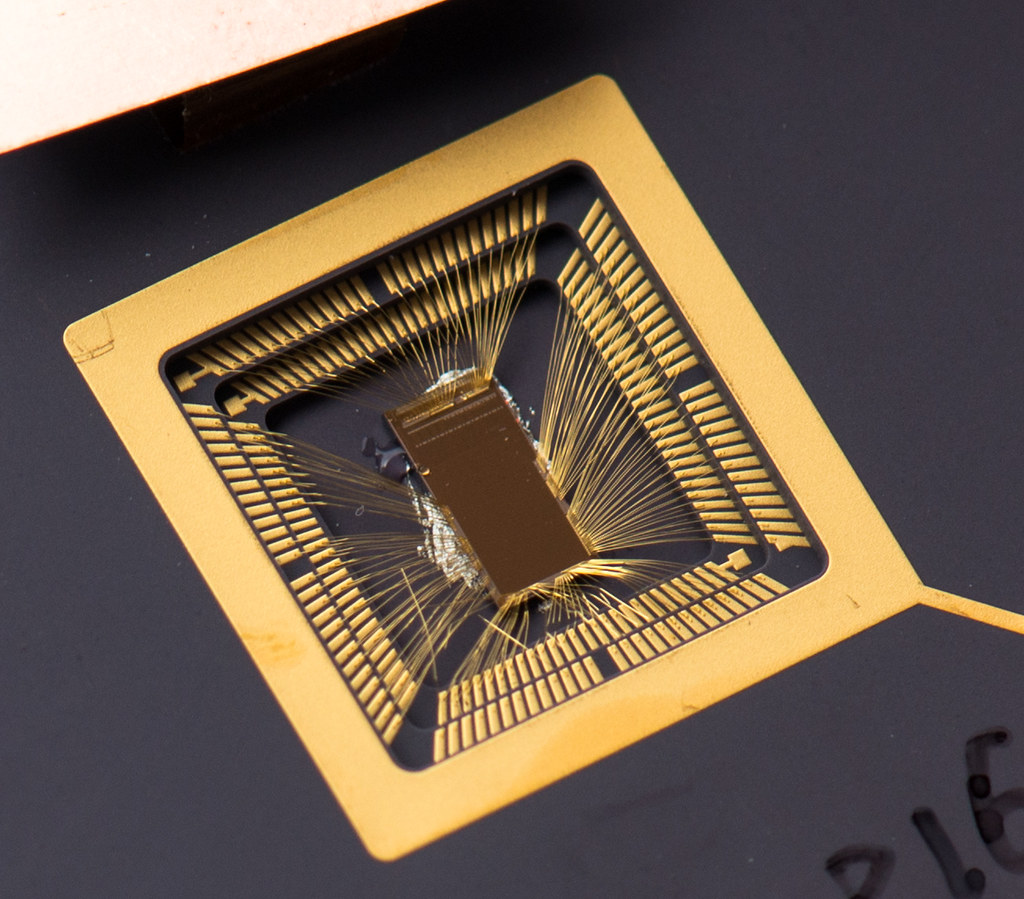

Dette design er meget enkelt, og dets formål er at udføre de første tests. Det blev lavet ved hjælp af en node af 65nm ved TSMC, nok til den relative enkelhed af denne tidlige prototype, der blev testet i nogle benchmarks for at se, hvad den var i stand til, og resultaterne var ret positive. Endnu bedre end forventet...

I maj 2019 ville det endelige design af denne chip blive sendt til EUROPRACTICE platform af EF, og derefter ville omkring 100 Lagarto-eksemplarer ankomme til Barcelona for at påbegynde testene og for at tjene som grundlag for acceleratoren for HPC, der også er baseret på denne ISA.

DRAC

Næste skridt var DRAC (Design af RISC-V-baserede acceleratorer til næste generation af computere). En chip designet til sikkerhedsapplikationer, såsom hardwarekryptering, såvel som videnskabelige applikationer såsom genomanalyse, simuleringsacceleration eller sektoren for autonome køretøjer.

Selvfølgelig er DRAC også ledet af BSC og er baseret på arkitekturen af RISC-V open source. Dette projekt forventes at vare omkring 3 år, hvor op til 40 forskere vil deltage og vil blive koordineret af Miquel Moretó, en forsker fra Ramón y Cajal-programmet ved UPC. Derudover har finansieringen været omkring 4 millioner euro, halvdelen fra FEDER-midler og den anden halvdel fra partnerne i dette projekt.

Dette er allerede begyndt at bære frugt. DVINO (DRAC Vector I-Order) Det er en første generations chip, der stammer fra dette projekt. Som navnet antyder, er det en IC i rækkefølge, der inkluderer en Lizard-kerne sammen med en Hydra-vektorprocessor designet til distribueret databehandling.

La anden generation forbedre chippens ydeevne med 15 % og tilføje nye controllere, og arealet er blevet øget op til 8.6 kvadratmillimeter.

e-processor

e-processor er det nye skridt fremad, en processor med versioner planlagt til supercomputing og servere, samt avancerede førerassistentsystemer til køretøjer (f.eks.: ADAS), IoT, mobile enheder mv.

Endnu en gang er BSC den, der er involveret i dette projekt. Det er det første open source europæiske full-stack økosystem, og hvis centrale søjle vil være en CPU baseret på RISC-V og med en kerne løber ud af drift. Barcelona-centret vil bidrage med sin erfaring i design af HDL IP-kerner, emulering og nødvendige værktøjer.

Sammen med BSC, andre vigtige medlemmer på europæisk plan, såsom Chalmers University of Technology, Foundation for Research and Technology Hellas, Universita degli Studi di Roma La Sapienza, Cortus, Christmann Informationstechnik, Universität Bielefeld, Extoll GmbH, Thales og Exapsys, samt støtte fra EuroHPC JU.

Der vil blive udviklet hardware- og softwareteknologier, som starter test på FPGA'er for derefter at give salatoen til ASIC'erne. Det første skridt vil være at designe en højtydende, højeffektiv RISC-V-kerne. Det vil være en single-core og en dual-core med sammenhængende link off-chip, selvom mere komplekse og kraftfulde design vil begynde senere. Den RISC-V baserede vektoraccelerator vil også blive designet, og traditionelle arbejdsbelastninger inden for supercomputing såsom bioinformatik, AI, HPDA osv. vil blive udforsket.

eProcessoren vil også være meget alsidig og fleksibel når den skaleres, for at kunne tilføje flere on-chip enheder.

Det næste trin: fremstilling

Designet af disse chips vil være europæisk, hvad der ikke vil være, er fremstillingen. Hvis Pearl er en fabelagtig, og givet efterslæbet med hensyn til fremstillingsknudepunkter fra støberier i medlemslandene, har designet været bestilt til TSMC, som vil fremstille den i 7nm-teknologi og ved hjælp af den nye 3D-pakketeknologi kaldet CoWoS (Chip-on-Wafer-on-Substrate).

Men tanken er ikke at være afhængig af udenlandske fabrikker til det, så det har EU også gjort mobiliserede en stor del af pengene til at finansiere opdateringen af halvlederfremstillingen i det gamle kontinent. Konkret vil den allokere 145.000 millioner euro med det formål at nå en node med 2nm produktionsteknologi på kort sigt.

Dette tager tid, og det er meningen, at det skal komme til 2-3 års udsigt. Derudover ser det ud til, at TSMC er med til at gøre dette muligt, og også det europæiske ASML, som er den førende producent af avancerede fotolitografimaskiner til halvlederindustrien, og som har base i Holland...

Nadia Calviño selv, Vice President of Economic Affairs and Digital Transformation, forklarede det sådan: «Der arbejdes på nationalt og internationalt plan for at se hvilke spanske og europæiske virksomheder der kan fremstille dem«, med henvisning til disse chips. I samme retning var Thierry Bretons tale i Europa-Kommissionen. Og det er, at de midler, der er allokeret til sektoren, i vid udstrækning vil komme fra den bistand, som EU yder til den digitale transformation og til det post-pandemiske opsving.