Europa ist stark von Technologien abhängig, die in den USA und China entwickelt und produziert werden. Deshalb bewegt sich seit einigen Jahren auf EU-Ebene einiges, damit dies nicht mehr der Fall ist und haben Unabhängigkeit, insbesondere in der Informatik. Aus diesen Bewegungen sind Projekte wie EPI, eProcessor, Unternehmen wie SiPearl sowie die GAIA-X-Infrastruktur entstanden.

Da die meisten ISAs oder Architekturen proprietär sind und sich außerhalb Europas befinden, Open Source Der Erfolg dieser Projekte war entscheidend. Das ISA RISC-V es hat Hoffnung geweckt und es diesen Prozessoren und Beschleunigern ermöglicht, darauf aufzubauen, ohne jegliche Einschränkung oder Einschränkung durch geopolitische und geostrategische Kriege.

EPI (European Processor Initiative) ist geboren

Eine der ersten Reaktionen Europas nach der Konferenz der EDA (European Defence Agency), bei der die Probleme der technologischen und industriellen Abhängigkeit der Mitgliedsländer aufgedeckt wurden, war die Initiierung einer gemeinsamen Initiative mit dem Namen EPI (Europäische Prozessorinitiative). Ihr Ziel ist es, ein Konsortium zusammenzubringen, um die notwendigen Mechanismen zu implementieren, um Prozessoren in Europa entwickeln zu lassen.

Diese Chips sind im Prinzip nicht für den privaten Gebrauch bestimmt, sondern konzentrieren sich auf der HPC-Sektor, also Supercomputing. Diese Hochleistungsmaschinen sind besonders kritisch, und als Ergebnis dieses Projekts werden EU-Rechenzentren ab 2023 auf Exascale hochgestuft. Sie werden auch in anderen Branchen wie der Automobil- und Luft- und Raumfahrtindustrie Anwendung finden.

Um dies zu ermöglichen, basierend auf RISC-V für Beschleuniger, während GPPs oder Allzweckprozessoren auf IP ARM Cortex Neoverse-Kernen basieren, da sie es ihnen ermöglichen, den Designprozess zu beschleunigen und nicht bei Null anzufangen.

EPI hat auch 26 Partner aus 10 verschiedenen europäischen Ländern, darunter Spanien. Eine der zentralen Säulen des Projekts ist das Barcelona National Supercomputing Centre (BCN). Zu Spanien gesellen sich Partner wie Chalmers Tekniska Hoegskola AB aus Schweden, Infineon Technologies aus Deutschland, CEA aus Frankreich, STMicroelectronics in Holland, die Università di Bologna in Italien, das Higher Technical Institute of Lissabon in Portugal, FORTH in Griechenland oder die ETH Labor Zürich aus der Schweiz.

SiPearl, das private Unternehmen, wird gegründet, um dem Projekt die Betriebsfähigkeit zu verleihen

Für den Betrieb wurde ein privates Unternehmen gegründet, das für die Verwaltung der aus diesem EPI-Projekt resultierenden Technologien verantwortlich ist. Er heißt JaPerle und der Hauptsitz befindet sich in Frankreich. Darüber hinaus haben sie eine Niederlassung in Deutschland und eine weitere in Spanien, speziell in Barcelona, eröffnet, um nah bei ihren BSC-Partnern zu sein.

Dieses Startup startete mit einem öffentlichen Budget von 80 millones de EUR, die nicht ausreichen, um alle Kosten zu decken, die ein so tiefgreifendes Projekt mit sich bringt. Daher wird SiPearl auch dafür verantwortlich sein, mehr als 100 Millionen Euro privat zu beschaffen, hauptsächlich aus Aktien.

Sein Mitbegründer und CEO, Philipp Notton, macht einen fantastischen Job, indem er einige Designer aus dem Silicon Valley rekrutiert, sowie die richtigen Mitarbeiter mit der Erfahrung, um dem Projekt alle Garantien zu geben. Sie suchen auch nach Technologiepartnern wie Graphcore, einem führenden britischen Unternehmen in Bezug auf die Beschleunigung von Chips mit künstlicher Intelligenz, die für HPC so wichtig sind.

BSC ein wichtiger Partner: Vom Lagarto-Chip bis zum Drac

El BSC (Barcelona Supercomputing Center) es ist ein Schlüsselstück dieses Projekts. Sie tragen nicht nur zum Design und zur Entwicklung dieser Prozessoren bei, sondern der Marenostrum 5 wird bereits damit beginnen, die Früchte dieses Projekts zu testen ...

Eidechse

Der erste spanische Mikroprozessor, der auf dem RISC-V-Befehlssatz basiert, wurde synchronisiert Eidechse, und es ist der erste Schritt zur technologischen Unabhängigkeit. Hinter diesem Projekt steckt jedoch eine große Anstrengung und Arbeit, die vom BSC des National Supercomputing Centre of Spain sowie der Zusammenarbeit des CSIC und des UPC koordiniert wird.

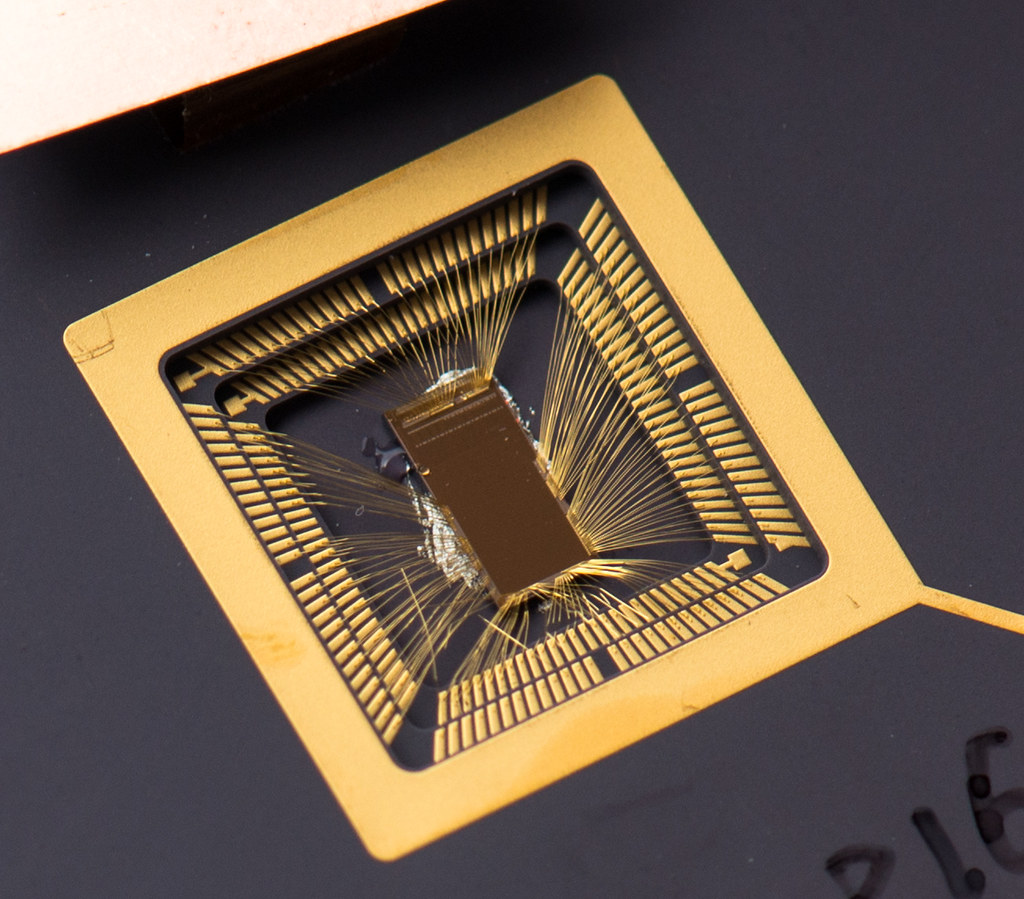

Dieses Design ist sehr einfach und Ihr Ziel ist es, die ersten Tests durchzuführen. Es wurde unter Verwendung eines Knotens von manufactured hergestellt 65 nm bei TSMC, genug für die relative Einfachheit dieses frühen Prototyps, dass er in einigen Benchmarks getestet wurde, um zu sehen, wozu er fähig ist, und die Ergebnisse waren recht positiv. Noch besser als erwartet...

Im Mai 2019 würde das endgültige Design dieses Chips an die EUROPRACTICE-Plattform der EG, und danach würden etwa 100 Exemplare von Lagarto in Barcelona eintreffen, um mit den Tests zu beginnen und als Basis für den Beschleuniger für den ebenfalls auf dieser ISA basierenden HPC zu dienen.

DRAC

Der nächste Schritt war DRAC (Entwurf von RISC-V-bsed-Beschleunigern für die Computer der nächsten Generation). Ein Chip, der für Sicherheitsanwendungen wie Hardwareverschlüsselung sowie wissenschaftliche Anwendungen wie Genomanalyse, Simulationsbeschleunigung oder den Bereich autonomer Fahrzeuge entwickelt wurde.

Natürlich wird auch DRAC von der BSC geleitet und basiert auf der Architektur von Open-Source-RISC-V. Dieses Projekt wird voraussichtlich etwa 3 Jahre dauern, an dem bis zu 40 Forscher teilnehmen werden und wird von Miquel Moretó, einem Forscher des Ramón y Cajal-Programms an der UPC, koordiniert. Darüber hinaus beläuft sich die Finanzierung auf rund 4 Millionen Euro, die Hälfte aus EFRE-Mitteln und die andere Hälfte von den Partnern dieses Projekts.

Dies hat sich bereits ausgezahlt. DVINO (DRAC-Vektor IN-Reihenfolge) Es ist ein aus diesem Projekt abgeleiteter Chip der ersten Generation. Wie der Name schon sagt, handelt es sich um einen wohlgeordneten IC, der einen Lagarto-Kern zusammen mit einem Hydra-Vektorprozessor enthält, der für verteiltes Rechnen entwickelt wurde.

La zweite Generation verbessern die Chipleistung um 15 % und fügen neue Treiber hinzu und vergrößern die Fläche auf 8.6 Quadratmillimeter.

eProzessor

eProzessor ist der neue Schritt nach vorne, ein Prozessor mit geplanten Versionen für Supercomputing und Server sowie fortschrittliche Fahrerassistenzsysteme für Fahrzeuge (zB: ADAS), IoT, mobile Geräte usw.

Auch hier ist die BSC derjenige, der an diesem Projekt beteiligt ist. Es ist das erste europäische Open-Source-Full-Stack-Ökosystem und dessen zentrale Säule wird eine CPU auf Basis von RISC-V und mit einem Kernel mit Out-of-Order-Execution. Das Zentrum in Barcelona wird seine Erfahrung im Design von IP-Cores in HDL, Emulation und den notwendigen Tools einbringen.

Zusammen mit der BSC, andere wichtige Mitglieder auf europäischer Ebene, wie die Chalmers University of Technology, die Foundation for Research and Technology Hellas, Universita degli Studi di Roma La Sapienza, Cortus, Christmann Informationstechnik, Universität Bielefeld, Extoll GmbH, Thales und Exapsys, sowie die Unterstützung von EuroHPC JU.

Hard- und Softwaretechnologien werden entwickelt und gestartet Testen auf FPGAs um dann den Salat an die ASICs zu geben. Der erste Schritt besteht darin, einen leistungsstarken, hocheffizienten RISC-V-Kern zu entwickeln. Es wird ein Single-Core und ein Dual-Core mit kohärenter Off-Chip-Verbindung sein, obwohl sie später mit komplexeren und leistungsfähigeren Designs beginnen werden. Der RISC-V-basierte Vektorbeschleuniger wird ebenfalls entworfen und traditionelle Supercomputing-Workloads wie Bioinformatik, KI, HPDA usw. untersucht.

Der eProzessor wird auch will sehr vielseitig und flexibel zum Zeitpunkt der Skalierung, um weitere Geräte auf dem Chip hinzufügen zu können.

Der nächste Schritt: Fertigung

Das Design dieser Chips wird europäisch sein, was nicht die Herstellung sein wird. SiPearl ist fabellos, und angesichts des Rückstands der Gießerei-Fertigungsknoten in den Mitgliedsländern wurde das Design beauftragt an TSMC, die es in 7-nm-Technologie und unter Verwendung der neuartigen 3D-Packaging-Technologie namens CoWoS (Chip-on-Wafer-on-Substrate) herstellen wird.

Die Idee ist jedoch, dafür nicht von ausländischen Fabriken abhängig zu sein, also hat die EU auch einen großen Teil des Geldes mobilisiert um die Modernisierung der Halbleiterfertigung auf dem alten Kontinent zu finanzieren. Konkret werden 145.000 Millionen Euro bereitgestellt, mit dem Ziel, kurzfristig einen Knoten mit 2-nm-Fertigungstechnologie zu erreichen.

Das braucht Zeit und soll erreicht werden 2-3 Jahre gesehen. Darüber hinaus scheint es, dass TSMC zusammenarbeitet, um dies zu ermöglichen, und auch die europäische ASML, die in den Niederlanden führend in der Herstellung fortschrittlicher Fotolithografiemaschinen für die Halbleiterindustrie ist ...

Nadia Calviño selbst, Vizepräsidentin für Wirtschaft und digitale Transformation, hat es so erklärt: «Auf nationaler und internationaler Ebene wird daran gearbeitet Sehen Sie, welche spanischen und europäischen Unternehmen sie herstellen können«, In Bezug auf diese Chips. In die gleiche Richtung ging die Rede von Thierry Breton vor der Europäischen Kommission. Und es ist so, dass die für den Sektor bestimmten Mittel größtenteils aus der Hilfe der EU für die digitale Transformation und für die Erholung nach der Pandemie stammen werden.