Eropa sangat bergantung pada teknologi yang dirancang dan diproduksi di Amerika Serikat dan Cina. Itulah sebabnya, dalam beberapa tahun terakhir, beberapa hal telah bergerak di tingkat UE sehingga hal ini tidak lagi terjadi, dan memiliki kemandirian, terutama dalam komputasi. Proyek seperti EPI, eProcessor, perusahaan seperti SiPearl, serta infrastruktur GAIA-X telah muncul dari pergerakan ini.

Karena sebagian besar ISA atau arsitektur adalah milik dan dimiliki di luar Eropa, sumber terbuka Ini telah menjadi kunci keberhasilan proyek-proyek ini. Itu ISA RISC-V itu telah membawa harapan, memungkinkan prosesor dan akselerator ini untuk membangunnya tanpa batasan atau batasan oleh perang geopolitik dan geostrategis.

EPI (Inisiatif Prosesor Eropa) lahir

Salah satu reaksi pertama Eropa, setelah konferensi EDA (Badan Pertahanan Eropa) di mana masalah ketergantungan teknologi dan industri negara-negara anggota terungkap, adalah untuk memulai inisiatif bersama yang disebut EPI (Inisiatif Prosesor Eropa). Tujuannya adalah untuk menyatukan sebuah konsorsium untuk menerapkan mekanisme yang diperlukan untuk memiliki prosesor yang dirancang di Eropa.

Chip ini, pada prinsipnya, tidak untuk penggunaan pribadi, tetapi akan fokus pada focus sektor HPC, yaitu, superkomputer. Mesin berperforma tinggi ini sangat penting, dan sebagai hasil dari proyek ini, pusat data UE akan dipromosikan ke Exascale mulai 2023. Mereka juga akan memiliki aplikasi di sektor lain seperti industri otomotif dan dirgantara.

Untuk memungkinkan ini, berdasarkan RISC-V untuk akselerator, sementara GPP atau prosesor tujuan umum akan didasarkan pada inti IP ARM Cortex Neoverse, karena mereka akan memungkinkan mereka untuk mempercepat proses desain dan tidak memulai dari awal.

EPI juga memiliki 26 mitra dari 10 negara Eropa yang berbeda, termasuk Spanyol. Salah satu pilar utama proyek ini adalah Barcelona National Supercomputing Center (BCN). Spanyol bergabung dengan mitra seperti Chalmers Tekniska Hoegskola AB dari Swedia, Infineon Technologies dari Jerman, CEA dari Prancis, STMicroelectronics di Belanda, Università di Bologna di Italia, Higher Technical Institute of Lisbon di Portugal, FORTH di Yunani, atau ETH laboratorium Zürich dari Swiss.

SiPearl, perusahaan swasta, dibuat untuk menyediakan proyek dengan kemampuan untuk beroperasi

Untuk beroperasi, telah dibuat perusahaan swasta yang akan bertugas mengelola teknologi yang dihasilkan dari proyek EPI ini. Namanya adalah SiMutiara dan kantor pusatnya berada di Prancis. Selain itu, mereka telah membuka anak perusahaan di Jerman dan satu lagi di Spanyol, khususnya di Barcelona, agar lebih dekat dengan mitra BSC mereka.

Startup ini dimulai dengan anggaran publik sebesar 80 juta euro, yang tidak cukup untuk menutupi semua biaya yang disiratkan oleh proyek dengan kedalaman seperti itu. Oleh karena itu, SiPearl juga akan bertanggung jawab untuk mengumpulkan lebih dari 100 juta euro secara pribadi, terutama dari saham.

Pendiri dan CEO-nya, Philippe Notton, melakukan pekerjaan yang fantastis dengan merekrut beberapa desainer yang didatangkan dari Silicon Valley, serta staf yang tepat dengan pengalaman untuk memberikan semua jaminan proyek. Mereka juga mencari mitra teknologi, seperti Graphcore, perusahaan Inggris terkemuka dalam hal akselerasi chip dengan kecerdasan buatan yang begitu penting di HPC.

BSC mitra utama: Dari chip Lagarto hingga Drac

El BSC (Pusat Komputer Super Barcelona) Ini adalah bagian penting dari proyek ini. Mereka tidak hanya berkontribusi pada desain dan pengembangan prosesor ini, tetapi Marenostrum 5 sudah akan mulai menguji buah dari proyek ini ...

Kadal

Mikroprosesor Spanyol pertama berdasarkan set instruksi RISC-V telah dijuluki Kadal, dan ini adalah langkah pertama untuk mencapai kemandirian teknologi. Namun, di balik proyek ini ada upaya besar dan kerja yang dikoordinasikan oleh BSC dari National Supercomputing Center of Spain, serta kolaborasi CSIC, dan UPC.

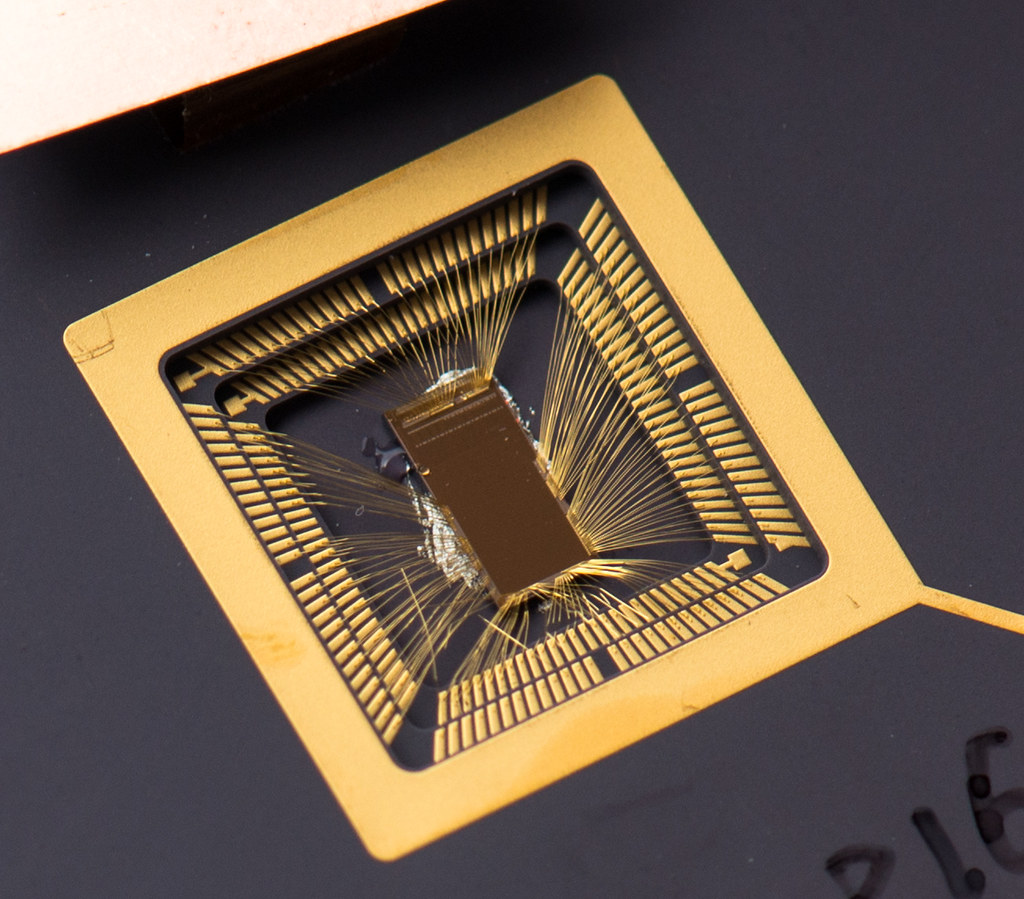

Desain ini sangat sederhana, dan tujuan Anda adalah melakukan tes pertama. Itu diproduksi menggunakan simpul 65nm di TSMC, cukup untuk kesederhanaan relatif dari prototipe awal ini sehingga diuji di beberapa tolok ukur untuk melihat kemampuannya, dan hasilnya cukup positif. Bahkan lebih baik dari yang diharapkan...

Pada Mei 2019 desain akhir chip ini akan dikirim ke Platform EROPA EC, dan setelah itu sekitar 100 eksemplar Lagarto akan tiba di Barcelona untuk memulai pengujian dan berfungsi sebagai basis akselerator untuk HPC yang juga didasarkan pada ISA ini.

Drak

Langkah selanjutnya adalah Drak (Merancang Akselerator berbasis RISC-V untuk Komputer generasi berikutnya). Sebuah chip yang dirancang untuk aplikasi keamanan, seperti enkripsi perangkat keras, serta aplikasi ilmiah seperti analisis genom, akselerasi simulasi, atau sektor kendaraan otonom.

Tentu saja, DRAC juga dipimpin oleh BSC dan didasarkan pada arsitektur sumber terbuka RISC-V. Proyek ini diperkirakan akan berlangsung sekitar 3 tahun, di mana hingga 40 peneliti akan berpartisipasi dan akan dikoordinasikan oleh Miquel Moretó, seorang peneliti dari program Ramón y Cajal di UPC. Selain itu, pembiayaannya sekitar 4 juta euro, setengah dari dana ERDF dan setengah lainnya dari mitra proyek ini.

Ini sudah mulai membuahkan hasil. DVINO (Urutan Vektor DRAC) Ini adalah chip yang berasal dari proyek ini dan dari generasi pertama. Seperti namanya, ini adalah IC yang tertata dengan baik yang mencakup inti Lagarto bersama dengan prosesor vektor Hydra yang dirancang untuk komputasi terdistribusi.

La generasi kedua meningkatkan kinerja chip sebesar 15% dan menambahkan driver baru serta meningkatkan area menjadi 8.6 milimeter persegi.

eProsesor

eProsesor adalah langkah maju baru, prosesor dengan versi yang direncanakan untuk superkomputer dan server, serta sistem bantuan pengemudi canggih untuk kendaraan (misalnya: ADAS), IoT, perangkat seluler, dll.

Sekali lagi BSC adalah orang yang terlibat dalam proyek ini. Ini adalah ekosistem full-stack open source Eropa pertama dan pilar utamanya adalah CPU berbasis RISC-V dan dengan kernel dengan eksekusi out-of-order. Pusat Barcelona akan menyumbangkan pengalamannya dalam desain inti IP dalam HDL, emulasi, dan alat yang diperlukan.

Bersama dengan BSC, lainnya anggota penting di tingkat Eropa, seperti Chalmers University of Technology, Foundation for Research and Technology Hellas, Universita degli Studi di Roma La Sapienza, Cortus, Christmann Informationstechnik, Universität Bielefeld, Extoll GmbH, Thales and Exapsys, serta dukungan dari EuroHPC JU.

Teknologi perangkat keras dan perangkat lunak akan dikembangkan dan dimulai pengujian pada FPGA untuk kemudian memberikan salat kepada ASIC. Langkah pertama adalah merancang inti RISC-V berperforma tinggi dan berefisiensi tinggi. Ini akan menjadi inti tunggal dan inti ganda dengan tautan off-chip yang koheren, meskipun kemudian mereka akan mulai dengan desain yang lebih kompleks dan kuat. Akselerator vektor berbasis RISC-V juga akan dirancang dan beban kerja komputasi super tradisional seperti bioinformatika, AI, HPDA, dll. akan dieksplorasi.

eProcessor juga akan menjadi sangat fleksibel dan fleksibel pada saat penskalaan, untuk dapat menambahkan lebih banyak perangkat on-chip.

Langkah selanjutnya: manufaktur

Desain chip ini akan menjadi Eropa, yang tidak adalah pembuatannya. SiPearl adalah dongeng, dan mengingat keterbelakangan dalam hal node manufaktur pengecoran di negara-negara anggota, desainnya telah ditugaskan ke TSMC, yang akan memproduksinya dalam teknologi 7nm dan menggunakan teknologi pengemasan 3D baru yang disebut CoWoS (Chip-on-Wafer-on-Substrate).

Namun, idenya adalah untuk tidak bergantung pada pabrik asing untuk itu, jadi UE juga memobilisasi sebagian besar uang untuk membiayai pembaruan manufaktur semikonduktor di Benua Lama. Secara khusus, ia akan mengalokasikan 145.000 juta euro, dengan tujuan mencapai simpul dengan teknologi manufaktur 2nm dalam jangka pendek.

Ini membutuhkan waktu, dan dimaksudkan untuk mencapai 2-3 tahun terlihat. Selain itu, tampaknya TSMC berkolaborasi untuk mewujudkannya, dan juga ASML Eropa, yang merupakan pemimpin dalam pembuatan mesin fotolitografi canggih untuk industri semikonduktor, dan yang berbasis di Belanda ...

Nadia Calviño sendiri, Vice President Economic Affairs and Digital Transformation telah menjelaskannya seperti ini: «Pekerjaan sedang dilakukan di tingkat nasional dan internasional untuk lihat perusahaan Spanyol dan Eropa mana yang dapat memproduksinya«, Mengacu pada chip ini. Dalam nada yang sama adalah pidato Thierry Breton di Komisi Eropa. Dan dana yang ditujukan untuk sektor ini sebagian besar akan berasal dari bantuan yang diberikan oleh UE untuk transformasi digital dan untuk pemulihan pascapandemi.