Europa jest silnie uzależniona od technologii zaprojektowanej i wyprodukowanej w Stanach Zjednoczonych i Chinach. Z tego powodu w ostatnich latach pewne rzeczy posuwają się do przodu na poziomie UE, tak że przestaje to mieć miejsce, i mieć niezależność, szczególnie w informatyce. Z tych ruchów powstały projekty takie jak EPI, eProcessor, firmy takie jak SiPearl, a także infrastruktura GAIA-X.

Ponieważ większość ISA lub architektur jest prawnie zastrzeżona i jest własnością poza Europą, otwarte źródło Powodzenie tych projektów było kluczowe. ISA RISC-V przyniósł nadzieję, pozwalając tym procesorom i akceleratorom budować na nim bez żadnych ograniczeń czy ograniczeń spowodowanych wojnami geopolitycznymi i geostrategicznymi.

Powstaje EPI (European Processor Initiative)

Jedną z pierwszych reakcji w Europie, po konferencji EDA (European Defence Agency), na której ujawniono problemy uzależnienia technologicznego i przemysłowego krajów członkowskich, było zainicjowanie wspólnej inicjatywy pn. EPI (europejska inicjatywa na rzecz procesorów). Jego celem jest zebranie konsorcjum w celu wdrożenia niezbędnych mechanizmów do projektowania procesorów w Europie.

Te chipy w zasadzie nie będą przeznaczone do użytku prywatnego, ale skupią się na sektor HPCczyli superkomputery. Te wysokowydajne maszyny mają szczególne znaczenie, a owoc tego projektu popchnie centra danych UE w kierunku Exascale od 2023 r. Będą one również miały zastosowanie w innych sektorach, takich jak przemysł motoryzacyjny i lotniczy.

Aby było to możliwe, na podstawie RISC-V dla akceleratorów, natomiast GPP czy procesory ogólnego przeznaczenia będą oparte na rdzeniach IP ARM Cortex Neoverse, ponieważ pozwolą im przyspieszyć proces projektowania, a nie zaczynać od zera.

EPI ma również 26 partnerów z 10 różnych krajów europejskich, w tym z Hiszpanii. Jednym z głównych filarów projektu jest Narodowe Centrum Superkomputerowe w Barcelonie (BCN). Do Hiszpanii dołączają partnerzy tacy jak Chalmers Tekniska Hoegskola AB ze Szwecji, Infineon Technologies z Niemiec, CEA z Francji, STMicroelectronics w Holandii, Uniwersytet Boloński we Włoszech, Wyższy Instytut Techniczny w Lizbonie w Portugalii, FORTH z Grecji czy ETH laboratorium Zürich ze Szwajcarii.

Powstaje prywatna firma SiPearl, która zapewnia projektowi możliwość działania

Aby działać, została utworzona prywatna firma, która będzie odpowiedzialna za zarządzanie technologiami wynikającymi z tego projektu EPI. Jego imię to Tak perła a jej siedziba znajduje się we Francji. Ponadto otworzyli filię w Niemczech i kolejną w Hiszpanii, a konkretnie w Barcelonie, aby być blisko swoich partnerów BSC.

Ten startup wystartował z budżetem publicznym w wysokości Millones 80 euro, które nie wystarczają na pokrycie wszystkich wydatków, jakie pociąga za sobą projekt o takiej głębokości. Dlatego SiPearl będzie również odpowiadał za prywatne zebranie ponad 100 mln euro, głównie z akcji.

Jej współzałożyciel i CEO, Filipa Nottona, wykonuje fantastyczną pracę, rekrutując kilku projektantów sprowadzonych z Doliny Krzemowej, a także odpowiednich pracowników z doświadczeniem, aby dać projektowi wszelkie gwarancje. Poszukują też partnerów technologicznych, takich jak Graphcore, wiodąca brytyjska firma zajmująca się przyspieszaniem układów ze sztuczną inteligencją, które są tak ważne w HPC.

BSC kluczowym partnerem: Od chipa Lagarto do Drac

El BSC (Centrum Superkomputerowe w Barcelonie) To kluczowy element tego projektu. Nie tylko przyczyniają się do projektowania i rozwoju tych procesorów, ale Marenostrum 5 już zacznie testować owoce tego projektu ...

Jaszczurka

Pierwszy hiszpański mikroprocesor oparty na zestawie instrukcji RISC-V został nazwany Jaszczurkai jest to pierwszy krok do osiągnięcia niezależności technologicznej. Jednak za tym projektem stoi ogromny wysiłek i praca koordynowana przez BSC Narodowego Centrum Superkomputerowego Hiszpanii, a także współpraca CSIC i UPC.

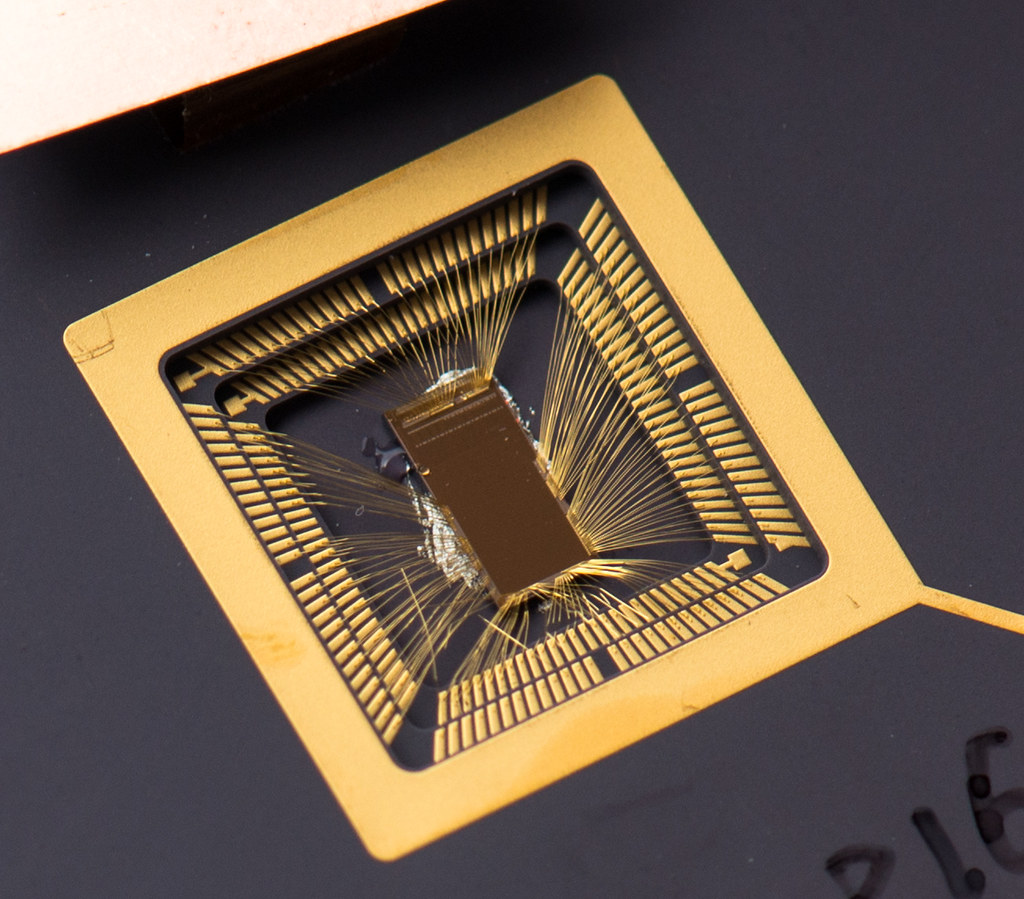

Ten projekt jest bardzo prosty, a Twoim celem jest przeprowadzenie pierwszych testów. Został wyprodukowany przy użyciu węzła 65 nm w TSMC, wystarczająco dla względnej prostoty tego wczesnego prototypu, że przetestowano go w niektórych benchmarkach, aby zobaczyć, do czego jest zdolny, a wyniki były całkiem pozytywne. Jeszcze lepiej niż oczekiwano...

W maju 2019 r. ostateczny projekt tego układu zostanie wysłany do Platforma EUROPRACTICE EC, a potem około 100 egzemplarzy Lagarto przyjedzie do Barcelony, aby rozpocząć testy i służyć jako podstawa akceleratora dla HPC, który również jest oparty na tej ISA.

DRAC

Następnym krokiem było DRAC (Projektowanie akceleratorów RISC-V-bsed dla komputerów nowej generacji). Chip przeznaczony do zastosowań związanych z bezpieczeństwem, takich jak szyfrowanie sprzętowe, a także do zastosowań naukowych, takich jak analiza genomu, przyspieszenie symulacji czy sektor pojazdów autonomicznych.

Oczywiście DRAC jest również zarządzany przez BSC i opiera się na architekturze open source RISC-V. Projekt ma trwać około 3 lata, w którym weźmie udział do 40 badaczy i będzie koordynowany przez Miquela Moretó, badacza z programu UPC Ramón y Cajal. Dodatkowo dofinansowanie wyniosło ok. 4 mln euro, połowa ze środków EFRR, a druga połowa od partnerów tego projektu.

To już zaczęło się opłacać. DVINO (w zamówieniu DRAC Vector) To chip wywodzący się z tego projektu i pierwszej generacji. Jak sama nazwa wskazuje, jest to dobrze uporządkowany układ scalony, który zawiera rdzeń Lagarto wraz z procesorem wektorowym Hydra przeznaczonym do obliczeń rozproszonych.

La drugie pokolenie popraw wydajność chipa o 15% i dodaj nowe sterowniki oraz zwiększ obszar do 8.6 milimetrów kwadratowych.

eProcesor

eProcesor to nowy krok naprzód, procesor z planowanymi wersjami dla superkomputerów i serwerów, a także zaawansowane systemy wspomagania kierowcy dla pojazdów (np.: ADAS), IoT, urządzenia mobilne itp.

Ponownie BSC jest tym, który jest zaangażowany w ten projekt. Jest to pierwszy europejski ekosystem typu full-stack typu open source, którego głównym filarem będzie procesor oparty na RISC-V i posiadający jądro z wykonaniem poza kolejnością. Centrum w Barcelonie wniesie swoje doświadczenie w projektowaniu rdzeni IP w HDL, emulacji i niezbędnych narzędziach.

Wraz z BSC inne ważni członkowie na poziomie europejskimtakich jak Chalmers University of Technology, Foundation for Research and Technology Hellas, Universita degli Studi di Roma La Sapienza, Cortus, Christmann Informationstechnik, Universität Bielefeld, Extoll GmbH, Thales and Exapsys, a także wsparcie EuroHPC JU.

Zostaną opracowane i uruchomione technologie sprzętowe i programowe testowanie na FPGA aby następnie dać salat ASICs. Pierwszym krokiem będzie zaprojektowanie wysokowydajnego, wysokosprawnego rdzenia RISC-V. Będzie to jednordzeniowy i dwurdzeniowy z spójnym łączem off-chip, chociaż później zaczną od bardziej złożonych i mocniejszych konstrukcji. Zaprojektowany zostanie również akcelerator wektorowy oparty na RISC-V i zbadane zostaną tradycyjne obciążenia obliczeniowe superkomputerów, takie jak bioinformatyka, sztuczna inteligencja, HPDA itp.

eProcessor będzie również bardzo wszechstronny i elastyczny w momencie skalowania, aby móc dodać więcej urządzeń na chipie.

Następny krok: produkcja

Projekt tych chipów będzie europejski, nie będzie to produkcja. SiPearl to fabless, a biorąc pod uwagę zaległości w węzłach odlewniczych w krajach członkowskich, projekt został zlecone TSMC, który wyprodukuje go w technologii 7 nm i przy użyciu nowatorskiej technologii pakowania 3D o nazwie CoWoS (Chip-on-Wafer-on-Substrate).

Nie chodzi jednak o to, by w tym celu polegać na zagranicznych fabrykach, więc UE ma również: zmobilizował sporą część pieniędzy na finansowanie modernizacji produkcji półprzewodników na Starym Kontynencie. W szczególności przeznaczy 145.000 2 milionów euro, aby w krótkim czasie dotrzeć do węzła z technologią produkcji XNUMX nm.

To wymaga czasu i ma na celu osiągnięcie Widoczne 2-3 lata. Ponadto wydaje się, że TSMC współpracuje, aby było to możliwe, a także europejski ASML, który jest liderem w produkcji zaawansowanych maszyn fotolitograficznych dla przemysłu półprzewodnikowego, a mający siedzibę w Holandii…

Sama Nadia Calviño, wiceprezes ds. gospodarki i transformacji cyfrowej wyjaśniła to w ten sposób: «Prace prowadzone są na poziomie krajowym i międzynarodowym, aby zobacz, jakie firmy hiszpańskie i europejskie mogą je wyprodukować«, W odniesieniu do tych żetonów. W tym samym duchu było przemówienie Thierry'ego Bretona w Komisji Europejskiej. A środki przeznaczone dla sektora będą pochodziły w dużej mierze z pomocy UE na transformację cyfrową i ożywienie po pandemii.