ยุโรปพึ่งพาเทคโนโลยีที่ออกแบบและผลิตในสหรัฐอเมริกาและจีนเป็นอย่างมาก ด้วยเหตุนี้ ในช่วงไม่กี่ปีที่ผ่านมา บางสิ่งได้เคลื่อนไหวในระดับสหภาพยุโรป เพื่อไม่ให้เป็นเช่นนี้ และ มีความเป็นอิสระโดยเฉพาะอย่างยิ่งในการคำนวณ. โครงการต่างๆ เช่น EPI, eProcessor, บริษัทต่างๆ เช่น SiPearl และโครงสร้างพื้นฐาน GAIA-X ได้เกิดขึ้นจากการเคลื่อนไหวเหล่านี้

เนื่องจาก ISA หรือสถาปัตยกรรมส่วนใหญ่เป็นกรรมสิทธิ์และเป็นเจ้าของนอกยุโรป โอเพ่นซอร์ส เป็นกุญแจสำคัญสำหรับโครงการเหล่านี้ที่จะประสบความสำเร็จ ไอเอสเอ RISC-V มันได้นำความหวัง ปล่อยให้โปรเซสเซอร์และตัวเร่งความเร็วเหล่านี้สร้างมันขึ้นมาโดยไม่มีข้อจำกัดหรือข้อจำกัดใดๆ จากสงครามภูมิรัฐศาสตร์และภูมิยุทธศาสตร์

EPI (European Processor Initiative) ถือกำเนิดขึ้น

หนึ่งในปฏิกิริยาแรกของยุโรป หลังจากการประชุม EDA (European Defense Agency) ที่ซึ่งปัญหาของการพึ่งพาทางเทคโนโลยีและอุตสาหกรรมของประเทศสมาชิกถูกเปิดเผย คือการริเริ่มความคิดริเริ่มร่วมกันที่เรียกว่า EPI (ผู้ริเริ่มโปรเซสเซอร์แห่งยุโรป). วัตถุประสงค์ของมันคือการรวมกลุ่มเพื่อใช้กลไกที่จำเป็นเพื่อให้มีโปรเซสเซอร์ที่ออกแบบในยุโรป

โดยหลักการแล้วชิปเหล่านี้จะไม่ใช้ส่วนตัว แต่จะเน้นที่ ภาค HPCนั่นคือซูเปอร์คอมพิวเตอร์ เครื่องจักรที่มีประสิทธิภาพสูงเหล่านี้มีความสำคัญอย่างยิ่ง และผลของโครงการนี้จะผลักดันศูนย์ข้อมูลของสหภาพยุโรปไปสู่ระดับ Exascale ตั้งแต่ปี 2023 นอกจากนี้ ยังจะนำไปใช้ในภาคส่วนอื่นๆ เช่น อุตสาหกรรมยานยนต์และอวกาศ

เพื่อให้สิ่งนี้เป็นไปได้ ขึ้นอยู่กับ RISC-V สำหรับตัวเร่งความเร็ว ในขณะที่ GPP หรือโปรเซสเซอร์วัตถุประสงค์ทั่วไปจะใช้แกน IP ของ ARM Cortex Neoverse เนื่องจากจะช่วยเพิ่มความเร็วในกระบวนการออกแบบและไม่เริ่มจากศูนย์

EPI ยังมี 26 พันธมิตรจาก 10 ประเทศในยุโรปต่าง ๆ รวมถึงสเปน. หนึ่งในเสาหลักของโครงการคือ Barcelona National Supercomputing Center (BCN) สเปนเข้าร่วมโดยพันธมิตร เช่น Chalmers Tekniska Hoegskola AB จากสวีเดน, Infineon Technologies จากเยอรมนี, CEA จากฝรั่งเศส, STMicroelectronics ในฮอลแลนด์, Università di Bologna ในอิตาลี, Higher Technical Institute of Lisbon ในโปรตุเกส, FORTH ในกรีซ หรือ ETH ห้องปฏิบัติการ Zürich จากสวิสเซอร์แลนด์

SiPearl บริษัทเอกชน จัดตั้งขึ้นเพื่อให้โครงการมีความสามารถในการดำเนินงาน

เพื่อดำเนินการ มีการจัดตั้งบริษัทเอกชนขึ้นซึ่งจะรับผิดชอบในการจัดการเทคโนโลยีที่เกิดจากโครงการ EPI นี้ ชื่อของเขาคือ เยสเพิร์ล และมีสำนักงานใหญ่อยู่ในฝรั่งเศส นอกจากนี้ พวกเขายังได้เปิดสาขาย่อยในเยอรมนีและอีกแห่งในสเปน โดยเฉพาะในบาร์เซโลนา เพื่อใกล้ชิดกับพันธมิตร BSC ของพวกเขา

การเริ่มต้นนี้เริ่มต้นด้วยงบประมาณสาธารณะของ 80 ล้านยูโรซึ่งไม่เพียงพอที่จะครอบคลุมค่าใช้จ่ายทั้งหมดที่เกี่ยวข้องกับโครงการที่มีความลึกดังกล่าว ดังนั้น SiPearl จะรับผิดชอบในการระดมทุนส่วนตัวมากกว่า 100 ล้านยูโร ส่วนใหญ่มาจากหุ้น

ผู้ร่วมก่อตั้งและซีอีโอ ฟิลิปป์ น็อตตัน, กำลังทำงานที่ยอดเยี่ยมในการสรรหานักออกแบบบางคนที่มาจาก Silicon Valley รวมถึงพนักงานที่เหมาะสมที่มีประสบการณ์เพื่อให้โครงการรับประกันทั้งหมด พวกเขายังมองหาพันธมิตรด้านเทคโนโลยี เช่น Graphcore บริษัทชั้นนำของอังกฤษในการเร่งชิปด้วยปัญญาประดิษฐ์ที่มีความสำคัญใน HPC

BSC พันธมิตรหลัก: จากชิป Lagarto ถึง Drac

El BSC (ศูนย์ซูเปอร์คอมพิวเตอร์บาร์เซโลนา) เป็นส่วนสำคัญของโครงการนี้ พวกเขาไม่เพียง แต่มีส่วนร่วมในการออกแบบและพัฒนาโปรเซสเซอร์เหล่านี้ แต่ Marenostrum 5 จะเริ่มทดสอบผลของโครงการนี้แล้ว ...

จิ้งจก

ไมโครโปรเซสเซอร์สเปนตัวแรกที่ใช้ชุดคำสั่ง RISC-V ได้รับการขนานนามว่า จิ้งจกและเป็นก้าวแรกสู่ความเป็นอิสระทางเทคโนโลยี อย่างไรก็ตาม เบื้องหลังโครงการนี้มีความพยายามและการทำงานร่วมกันอย่างมากโดย BSC ของ National Supercomputing Center of Spain รวมถึงความร่วมมือของ CSIC และ UPC

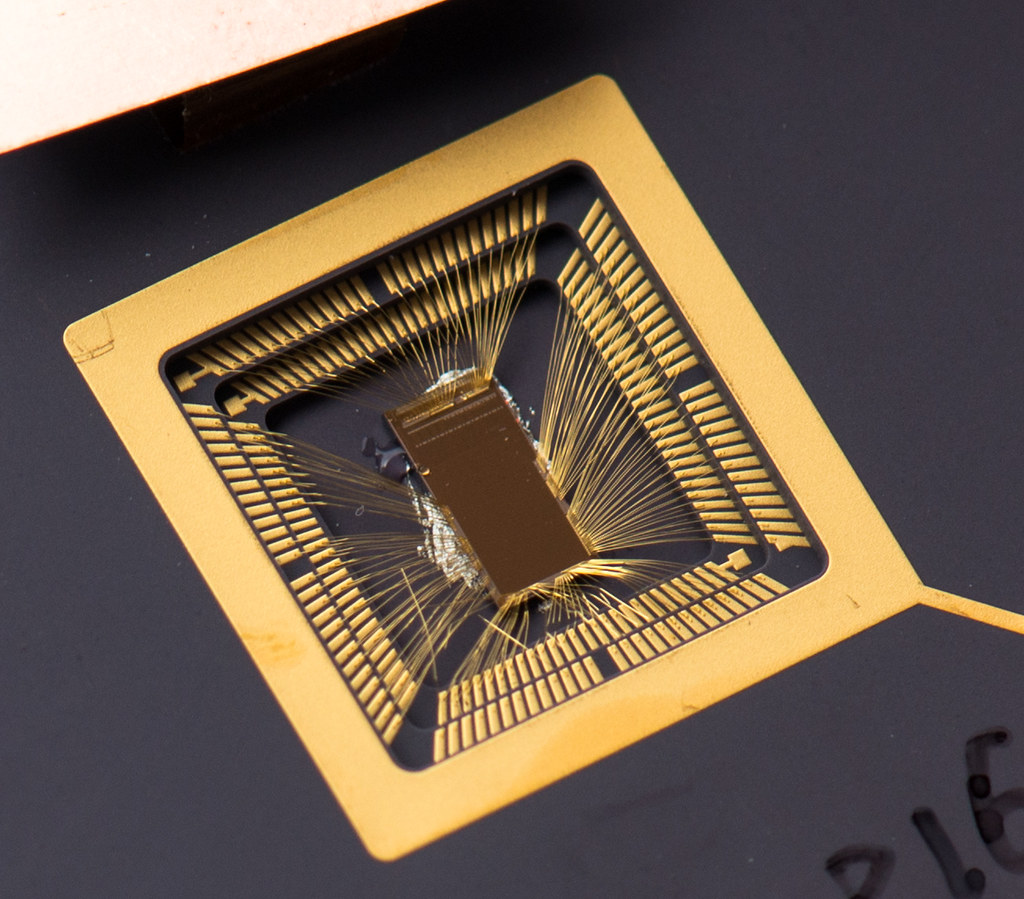

การออกแบบนี้ง่ายมาก และเป้าหมายของคุณคือทำการทดสอบครั้งแรก มันถูกผลิตขึ้นโดยใช้โหนด 65nm ที่TSMCเพียงพอสำหรับความเรียบง่ายสัมพัทธ์ของต้นแบบรุ่นแรกนี้ซึ่งได้รับการทดสอบในเกณฑ์มาตรฐานบางอย่างเพื่อดูว่าสามารถทำอะไรได้บ้าง และผลลัพธ์ก็ค่อนข้างดี ดีเกินคาด ...

ในเดือนพฤษภาคม 2019 การออกแบบขั้นสุดท้ายของชิปนี้จะถูกส่งไปยัง แพลตฟอร์ม EUROPRACTICE ของ EC และหลังจากนั้นประมาณ 100 สำเนาของ Lagarto จะมาถึงบาร์เซโลนาเพื่อเริ่มต้นด้วยการทดสอบและเพื่อใช้เป็นฐานสำหรับตัวเร่งความเร็วสำหรับ HPC ที่ใช้ ISA นี้ด้วย

ดีอาร์เอซี

ขั้นตอนต่อไปคือ ดีอาร์เอซี (การออกแบบตัวเร่งความเร็ว RISC-V-bsed สำหรับคอมพิวเตอร์รุ่นต่อไป) ชิปที่ออกแบบมาสำหรับแอปพลิเคชันด้านความปลอดภัย เช่น การเข้ารหัสฮาร์ดแวร์ เช่นเดียวกับแอปพลิเคชันทางวิทยาศาสตร์ เช่น การวิเคราะห์จีโนม การเร่งการจำลอง หรือภาคยานยนต์อิสระ

แน่นอน DRAC ยังนำโดย BSC และขึ้นอยู่กับสถาปัตยกรรมของ โอเพ่นซอร์ส RISC-V. โครงการนี้มีกำหนดใช้เวลาประมาณ 3 ปี โดยจะมีนักวิจัยเข้าร่วมมากถึง 40 คนและจะประสานงานโดย Miquel Moretó นักวิจัยจากโครงการ UPC Ramón y Cajal นอกจากนี้ การจัดหาเงินทุนยังได้รับประมาณ 4 ล้านยูโร โดยครึ่งหนึ่งมาจากกองทุน ERDF และอีกครึ่งหนึ่งมาจากพันธมิตรของโครงการนี้

นี้ได้เริ่มชำระแล้ว DVINO (DRAC Vector ตามลำดับ) เป็นชิปที่ได้มาจากโปรเจ็กต์นี้และรุ่นแรก ตามชื่อของมัน มันเป็น IC ที่ได้รับคำสั่งอย่างดีซึ่งมีแกน Lagarto ร่วมกับโปรเซสเซอร์ไฮดราเวคเตอร์ที่ออกแบบมาสำหรับการคำนวณแบบกระจาย

La รุ่นที่สอง ปรับปรุงประสิทธิภาพของชิป 15% และเพิ่มไดรเวอร์ใหม่และเพิ่มพื้นที่เป็น 8.6 ตารางมิลลิเมตร

อีโปรเซสเซอร์

อีโปรเซสเซอร์ เป็นขั้นตอนต่อไป โปรเซสเซอร์ที่มีเวอร์ชันที่วางแผนไว้สำหรับซูเปอร์คอมพิวเตอร์และเซิร์ฟเวอร์ ตลอดจนระบบช่วยเหลือผู้ขับขี่ขั้นสูงสำหรับยานพาหนะ (เช่น ADAS), IoT, อุปกรณ์เคลื่อนที่ ฯลฯ

อีกครั้งที่ BSC เป็นผู้มีส่วนร่วมในโครงการนี้ เป็นระบบนิเวศแบบฟูลสแตกแบบโอเพ่นซอร์สแห่งแรกของยุโรปและมีเสาหลักหลักคือซีพียูที่ใช้ RISC-V และด้วย เคอร์เนลที่มีการดำเนินการนอกคำสั่ง. ศูนย์บาร์เซโลนาจะมอบประสบการณ์ในการออกแบบแกน IP ใน HDL การจำลอง และเครื่องมือที่จำเป็น

พร้อมด้วย BSC อื่นๆ สมาชิกสำคัญระดับยุโรปเช่น Chalmers University of Technology, มูลนิธิเพื่อการวิจัยและเทคโนโลยี Hellas, Universita degli Studi di Roma La Sapienza, Cortus, Christmann Informationstechnik, Universität Bielefeld, Extoll GmbH, Thales และ Exapsys ตลอดจนการสนับสนุนของ EuroHPC JU

เทคโนโลยีฮาร์ดแวร์และซอฟต์แวร์จะได้รับการพัฒนาและเริ่มต้น การทดสอบ FPGAs จากนั้นให้ละหมาดแก่ ASICs ขั้นตอนแรกคือการออกแบบแกน RISC-V ที่มีประสิทธิภาพสูง มันจะเป็น single-core และ dual-core พร้อม off-chip link ที่เชื่อมโยงกัน แม้ว่าในภายหลังพวกเขาจะเริ่มต้นด้วยการออกแบบที่ซับซ้อนและมีประสิทธิภาพมากขึ้น นอกจากนี้ ตัวเร่งความเร็วเวกเตอร์ที่ใช้ RISC-V จะได้รับการออกแบบและจะมีการสำรวจปริมาณงานซูเปอร์คอมพิวเตอร์แบบดั้งเดิม เช่น ชีวสารสนเทศ, AI, HPDA เป็นต้น

eProcessor จะเป็น อเนกประสงค์และยืดหยุ่นมาก ในขณะที่ทำการปรับขนาดเพื่อให้สามารถเพิ่มอุปกรณ์บนชิปได้มากขึ้น

ขั้นตอนต่อไป: การผลิต

การออกแบบชิปเหล่านี้จะเป็นแบบยุโรป สิ่งที่จะไม่เป็นคือการผลิต SiPearl เป็นนิทานและด้วยความล้าหลังในแง่ของโหนดการผลิตโรงหล่อในประเทศสมาชิกการออกแบบได้รับ มอบหมายให้ TSMCซึ่งจะผลิตในเทคโนโลยี 7nm และใช้เทคโนโลยีบรรจุภัณฑ์ 3D ใหม่ที่เรียกว่า CoWoS (Chip-on-Wafer-on-Substrate)

อย่างไรก็ตาม แนวคิดนี้ไม่ได้ขึ้นอยู่กับโรงงานของต่างประเทศ ดังนั้นสหภาพยุโรปก็มี has ระดมเงินเป็นจำนวนมาก เพื่อเป็นเงินทุนในการปรับปรุงการผลิตเซมิคอนดักเตอร์ในทวีปเก่า โดยเฉพาะอย่างยิ่งจะจัดสรร 145.000 ล้านยูโรโดยมีเป้าหมายเพื่อเข้าถึงโหนดที่มีเทคโนโลยีการผลิต 2 นาโนเมตรในระยะสั้น

ต้องใช้เวลาและตั้งใจจะไปถึง ผ่านไป 2-3 ปี. นอกจากนี้ ดูเหมือนว่า TSMC กำลังร่วมมือกันเพื่อทำให้สิ่งนี้เป็นไปได้ รวมถึง ASML ของยุโรป ซึ่งเป็นผู้นำในการผลิตเครื่อง photolithography ขั้นสูงสำหรับอุตสาหกรรมเซมิคอนดักเตอร์และซึ่งตั้งอยู่ในประเทศเนเธอร์แลนด์ ...

Nadia Calviño รองประธานฝ่ายเศรษฐกิจและการเปลี่ยนแปลงทางดิจิทัลได้อธิบายไว้ดังนี้: «งานกำลังดำเนินการในระดับชาติและระดับนานาชาติเพื่อ ดูว่าบริษัทใดในสเปนและยุโรปสามารถผลิตได้« ในการอ้างอิงถึงชิปเหล่านี้ ในทำนองเดียวกัน สุนทรพจน์ของ Thierry Breton ที่คณะกรรมาธิการยุโรป และก็คือว่าเงินทุนที่ส่งไปยังภาคส่วนส่วนใหญ่จะมาจากความช่วยเหลือจากสหภาพยุโรปสำหรับการเปลี่ยนแปลงทางดิจิทัลและการฟื้นตัวหลังการระบาด