Châu Âu phụ thuộc nhiều vào công nghệ được thiết kế và sản xuất tại Hoa Kỳ và Trung Quốc. Đó là lý do tại sao, trong một vài năm, một số điều đã được di chuyển ở cấp độ EU để điều này không còn xảy ra, và có tính độc lập, đặc biệt là trong lĩnh vực máy tính. Các dự án như EPI, eProcessor, các công ty như SiPearl, cũng như cơ sở hạ tầng GAIA-X đã xuất hiện từ những phong trào này.

Vì hầu hết các ISA hoặc kiến trúc đều thuộc quyền sở hữu và sở hữu bên ngoài Châu Âu, mã nguồn mở Đó là chìa khóa để những dự án này thành công. Các ISA RISC-V nó đã mang lại hy vọng, cho phép các bộ xử lý và máy gia tốc này xây dựng dựa trên nó mà không bị hạn chế hoặc hạn chế bởi các cuộc chiến tranh địa chính trị và địa chiến lược.

EPI (European Processor Initiative) ra đời

Một trong những phản ứng đầu tiên của châu Âu, sau hội nghị EDA (Cơ quan Quốc phòng châu Âu), nơi các vấn đề về sự phụ thuộc công nghệ và công nghiệp của các nước thành viên được phơi bày, là khởi xướng một sáng kiến chung có tên EPI (Sáng kiến Bộ xử lý Châu Âu). Mục tiêu của nó là tập hợp một tập đoàn để thực hiện các cơ chế cần thiết để có các bộ xử lý được thiết kế ở Châu Âu.

Về nguyên tắc, những con chip này sẽ không được sử dụng cho mục đích cá nhân, mà sẽ tập trung vào lĩnh vực HPC, tức là, siêu máy tính. Những cỗ máy hiệu suất cao này đặc biệt quan trọng và kết quả của dự án này, các trung tâm dữ liệu của EU sẽ được nâng cấp lên Exascale từ năm 2023. Chúng cũng sẽ được ứng dụng trong các lĩnh vực khác như công nghiệp ô tô và hàng không vũ trụ.

Để biến điều này thành khả thi, dựa trên RISC-V đối với bộ tăng tốc, trong khi GPP hoặc bộ xử lý đa năng sẽ dựa trên lõi IP ARM Cortex Neoverse, vì chúng sẽ cho phép chúng tăng tốc quá trình thiết kế và không phải bắt đầu lại từ đầu.

EPI cũng có 26 đối tác từ 10 quốc gia châu Âu khác nhau, bao gồm cả Tây Ban Nha. Một trong những trụ cột trung tâm của dự án là Trung tâm Siêu máy tính Quốc gia Barcelona (BCN). Tây Ban Nha có sự tham gia của các đối tác như Chalmers Tekniska Hoegskola AB từ Thụy Điển, Infineon Technologies từ Đức, CEA từ Pháp, STMicroelectronics ở Hà Lan, Università di Bologna ở Ý, Học viện kỹ thuật cao hơn của Lisbon ở Bồ Đào Nha, FORTH ở Hy Lạp hoặc ETH phòng thí nghiệm Zürich từ Thụy Sĩ.

SiPearl, công ty tư nhân, được thành lập để cung cấp cho dự án khả năng hoạt động

Để hoạt động, một công ty tư nhân đã được thành lập sẽ chịu trách nhiệm quản lý các công nghệ thu được từ dự án EPI này. Tên anh ta là CóPearl và trụ sở chính của nó ở Pháp. Ngoài ra, họ đã mở một công ty con ở Đức và một công ty con khác ở Tây Ban Nha, cụ thể là ở Barcelona, để gần gũi với các đối tác BSC của họ.

Công ty khởi nghiệp này bắt đầu với ngân sách công là 80 hàng triệu euro, không đủ để trang trải tất cả các chi phí mà một dự án có chiều sâu như vậy ngụ ý. Do đó, SiPearl cũng sẽ phụ trách riêng việc huy động hơn 100 triệu euro, chủ yếu từ cổ phiếu.

Người đồng sáng lập và Giám đốc điều hành của nó, philippe notton, đang thực hiện một công việc tuyệt vời khi tuyển dụng một số nhà thiết kế được đưa đến từ Thung lũng Silicon, cũng như đội ngũ nhân viên phù hợp với kinh nghiệm để đảm bảo cho dự án. Họ cũng đang tìm kiếm các đối tác công nghệ, chẳng hạn như Graphcore, một công ty hàng đầu của Anh về tăng tốc chip với trí tuệ nhân tạo rất quan trọng ở HPC.

BSC một đối tác chính: Từ chip Lagarto đến Drac

El BSC (Trung tâm Siêu máy tính Barcelona) nó là một phần quan trọng của dự án này. Họ không chỉ đóng góp vào việc thiết kế và phát triển các bộ vi xử lý này, mà Marenostrum 5 sẽ bắt đầu thử nghiệm thành quả của dự án này ...

Con thằn lằn

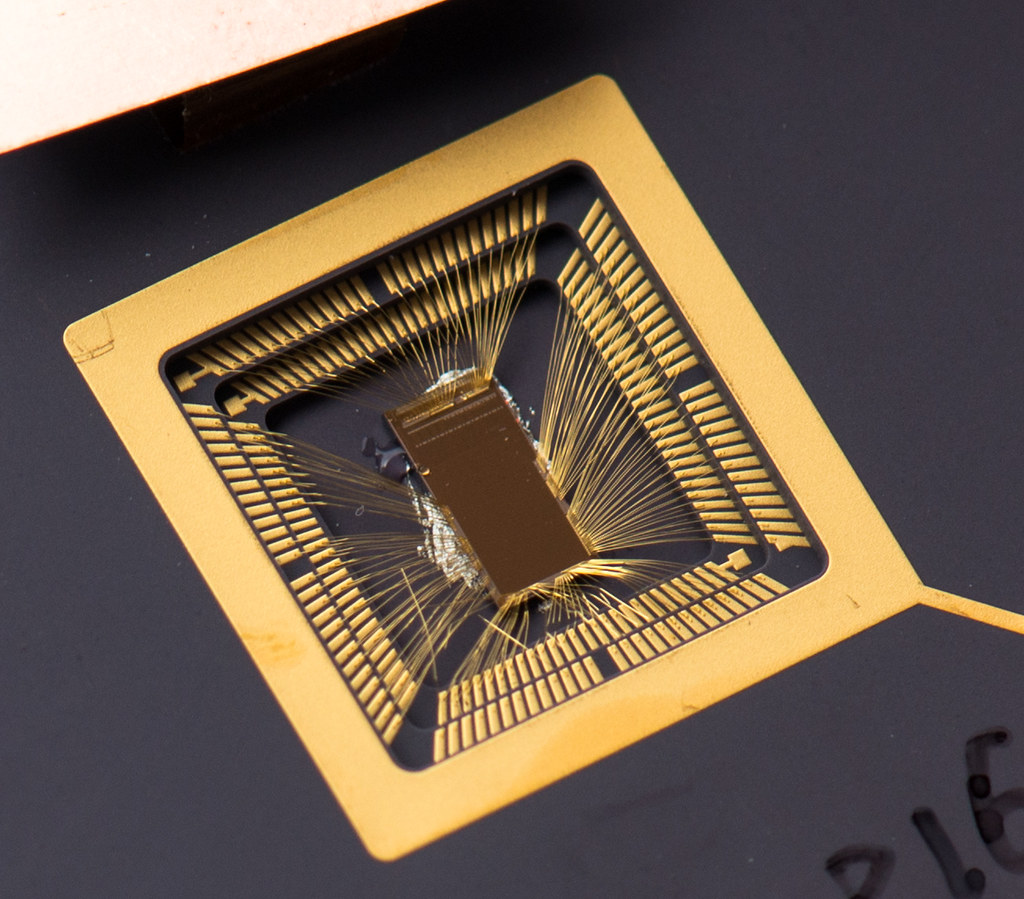

Bộ vi xử lý đầu tiên của Tây Ban Nha dựa trên tập lệnh RISC-V đã được đặt tên là Con thằn lằn, và đó là bước đầu tiên để đạt được sự độc lập về công nghệ. Tuy nhiên, đằng sau dự án này có một nỗ lực và công việc lớn được điều phối bởi BSC của Trung tâm Siêu máy tính Quốc gia Tây Ban Nha, cũng như sự hợp tác của CSIC và UPC.

Thiết kế này rất đơn giản và mục tiêu của bạn là thực hiện các thử nghiệm đầu tiên. Nó được sản xuất bằng cách sử dụng một nút của 65nm ở TSMC, đủ cho sự đơn giản tương đối của nguyên mẫu ban đầu này rằng nó đã được thử nghiệm trong một số tiêu chuẩn để xem nó có khả năng gì và kết quả khá khả quan. Thậm chí còn tốt hơn mong đợi ...

Vào tháng 2019 năm XNUMX, thiết kế cuối cùng của con chip này sẽ được gửi đến Nền tảng EUROPRACTICE của EC, và sau đó khoảng 100 bản sao của Lagarto sẽ đến Barcelona để bắt đầu các bài kiểm tra và làm cơ sở cho bộ tăng tốc cho HPC cũng dựa trên ISA này.

DRAC

Bước tiếp theo là DRAC (Thiết kế Bộ tăng tốc RISC-V-bsed cho Máy tính thế hệ tiếp theo). Một con chip được thiết kế cho các ứng dụng bảo mật, chẳng hạn như mã hóa phần cứng, cũng như các ứng dụng khoa học như phân tích bộ gen, tăng tốc mô phỏng hoặc lĩnh vực xe tự hành.

Tất nhiên, DRAC cũng được dẫn dắt bởi BSC và dựa trên kiến trúc của mã nguồn mở RISC-V. Dự án này dự kiến kéo dài khoảng 3 năm, trong đó có tới 40 nhà nghiên cứu sẽ tham gia và sẽ được điều phối bởi Miquel Moretó, một nhà nghiên cứu từ chương trình Ramón y Cajal tại UPC. Ngoài ra, khoản tài trợ khoảng 4 triệu euro, một nửa từ quỹ ERDF và nửa còn lại từ các đối tác của dự án này.

Điều này đã bắt đầu thành công. DVINO (Véc tơ DRAC theo thứ tự) Nó là một con chip có nguồn gốc từ dự án này và của thế hệ đầu tiên. Đúng như tên gọi, nó là một vi mạch được sắp xếp hợp lý bao gồm lõi Lagarto cùng với bộ xử lý vector Hydra được thiết kế cho tính toán phân tán.

La thế hệ thứ hai cải thiện hiệu suất chip lên 15% và thêm trình điều khiển mới và tăng diện tích lên 8.6 mm vuông.

bộ xử lý điện tử

bộ xử lý điện tử là một bước tiến mới, một bộ xử lý với các phiên bản được lên kế hoạch cho siêu máy tính và máy chủ, cũng như các hệ thống hỗ trợ lái xe tiên tiến cho phương tiện (ví dụ: ADAS), IoT, thiết bị di động, v.v.

Một lần nữa BSC là người tham gia vào dự án này. Đây là hệ sinh thái full-stack nguồn mở đầu tiên của Châu Âu và trụ cột trung tâm của nó sẽ là CPU dựa trên RISC-V và với kernel với việc thực thi không theo thứ tự. Trung tâm Barcelona sẽ đóng góp kinh nghiệm của mình trong việc thiết kế các lõi IP trong HDL, mô phỏng và các công cụ cần thiết.

Cùng với BSC, các các thành viên quan trọng ở cấp độ Châu Âu, chẳng hạn như Đại học Công nghệ Chalmers, Quỹ Nghiên cứu và Công nghệ Hellas, Universita degli Studi di Roma La Sapienza, Cortus, Christmann Informationstechnik, Universität Bielefeld, Extoll GmbH, Thales và Exapsys, cũng như sự hỗ trợ của EuroHPC JU.

Công nghệ phần cứng và phần mềm sẽ được phát triển và khởi động thử nghiệm trên FPGA sau đó đưa salat cho ASIC. Bước đầu tiên sẽ là thiết kế một lõi RISC-V hiệu suất cao, hiệu suất cao. Nó sẽ là lõi đơn và lõi kép với liên kết mạch lạc ngoài chip, mặc dù sau này chúng sẽ bắt đầu với những thiết kế phức tạp và mạnh mẽ hơn. Máy gia tốc vector dựa trên RISC-V cũng sẽ được thiết kế và các khối lượng công việc siêu máy tính truyền thống như tin sinh học, AI, HPDA, v.v. sẽ được khám phá.

Bộ xử lý điện tử cũng sẽ rất linh hoạt và linh hoạt tại thời điểm mở rộng quy mô, để có thể thêm nhiều thiết bị trên chip.

Bước tiếp theo: sản xuất

Thiết kế của những con chip này sẽ là Châu Âu, những gì sẽ không phải là sản xuất. SiPearl là một công ty tuyệt vời, và do tồn đọng các nút sản xuất đúc ở các nước thành viên, thiết kế đã ủy quyền cho TSMC, sẽ sản xuất nó theo công nghệ 7nm và sử dụng công nghệ đóng gói 3D mới lạ được gọi là CoWoS (Chip-on-Wafer-on-Substrate).

Tuy nhiên, ý tưởng là không phụ thuộc vào các nhà máy nước ngoài, vì vậy EU cũng đã huy động một phần lớn tiền để tài trợ cho việc cập nhật sản xuất chất bán dẫn ở Lục địa già. Cụ thể, nó sẽ phân bổ 145.000 triệu euro, với mục tiêu đạt được một điểm nút với công nghệ sản xuất 2nm trong thời gian ngắn.

Điều này cần có thời gian và nhằm đạt được 2-3 năm nhìn thấy. Ngoài ra, có vẻ như TSMC đang hợp tác để biến điều này thành hiện thực, và ASML của Châu Âu, công ty dẫn đầu trong việc sản xuất các máy quang khắc tiên tiến cho ngành công nghiệp bán dẫn và có trụ sở tại Hà Lan ...

Bản thân Nadia Calviño, Phó chủ tịch phụ trách các vấn đề kinh tế và chuyển đổi kỹ thuật số đã giải thích như thế này: «Công việc đang được thực hiện ở cấp quốc gia và quốc tế để xem các công ty Tây Ban Nha và Châu Âu nào có thể sản xuất chúng«, Liên quan đến những con chip này. Tương tự là bài phát biểu của Thierry Breton tại Ủy ban Châu Âu. Và đó là nguồn vốn dành cho lĩnh vực này phần lớn sẽ đến từ viện trợ do EU cung cấp cho quá trình chuyển đổi kỹ thuật số và phục hồi sau đại dịch.