歐洲嚴重依賴美國和中國設計和生產的技術。 這就是為什麼幾年來,歐盟層面上的一些事情一直在發生變化,從而不再是這種情況,並且 具有獨立性,尤其是在計算方面. EPI、eProcessor 等項目、SiPearl 等公司以及 GAIA-X 基礎設施都從這些運動中湧現。

由於大多數 ISA 或架構是專有的並且在歐洲以外擁有, 開源 這是這些項目取得成功的關鍵。 這 精簡指令集-V 它帶來了希望,允許這些處理器和加速器在其基礎上發展,而不受地緣政治和地緣戰略戰爭的任何限製或限制。

EPI(歐洲處理器倡議)誕生

在暴露成員國技術和工業依賴問題的 EDA(歐洲防務署)會議之後,歐洲的第一反應之一是發起一項名為 EPI(歐洲處理器倡議). 其目標是召集一個財團來實施必要的機制,以便在歐洲設計處理器。

這些芯片原則上不會供私人使用,而是專注於 高性能計算領域,也就是超級計算。 這些高性能機器尤其重要,作為該項目的結果,歐盟數據中心將從 2023 年起升級為 Exascale。它們還將應用於汽車和航空航天工業等其他領域。

為了使這成為可能, 基於RISC-V 對於加速器,而 GPP 或通用處理器將基於 ARM Cortex Neoverse IP 內核,因為它們將允許它們加快設計過程,而不是從頭開始。

EPI也有 來自包括西班牙在內的 26 個不同歐洲國家的 10 個合作夥伴. 該項目的核心支柱之一是巴塞羅那國家超級計算中心 (BCN)。 西班牙的合作夥伴包括瑞典的 Chalmers Tekniska Hoegskola AB、德國的英飛凌科技、法國的 CEA、荷蘭的意法半導體、意大利的博洛尼亞大學、葡萄牙的里斯本高等技術學院、希臘的 FORTH 或 ETH瑞士蘇黎世實驗室。

SiPearl 是一家私營公司,旨在為項目提供運營能力

為了運營,創建了一家私營公司,負責管理該 EPI 項目產生的技術。 他的名字是 珍珠 其總部在法國。 此外,他們在德國和西班牙分別開設了一家子公司,特別是在巴塞羅那,以貼近他們的 BSC 合作夥伴。

這家初創公司的公共預算為 80百萬歐元,這不足以支付如此深度的項目所隱含的所有費用。 因此,SiPearl 也將負責私人籌集超過 100 億歐元,主要來自股票。

它的聯合創始人兼首席執行官, 菲利普·諾頓,正在招聘一些從矽谷引進的設計師,以及有經驗的合適員工,為項目提供所有保證。 他們還在尋找技術合作夥伴,例如 Graphcore,這是一家領先的英國公司,致力於利用在 HPC 中非常重要的人工智能加速芯片。

BSC 關鍵合作夥伴:從 Lagarto 芯片到 Drac

El BSC(巴塞羅那超級計算中心) 它是這個項目的關鍵部分。 他們不僅為這些處理器的設計和開發做出了貢獻,而且 Marenostrum 5 已經開始測試這個項目的成果......

蜥蜴

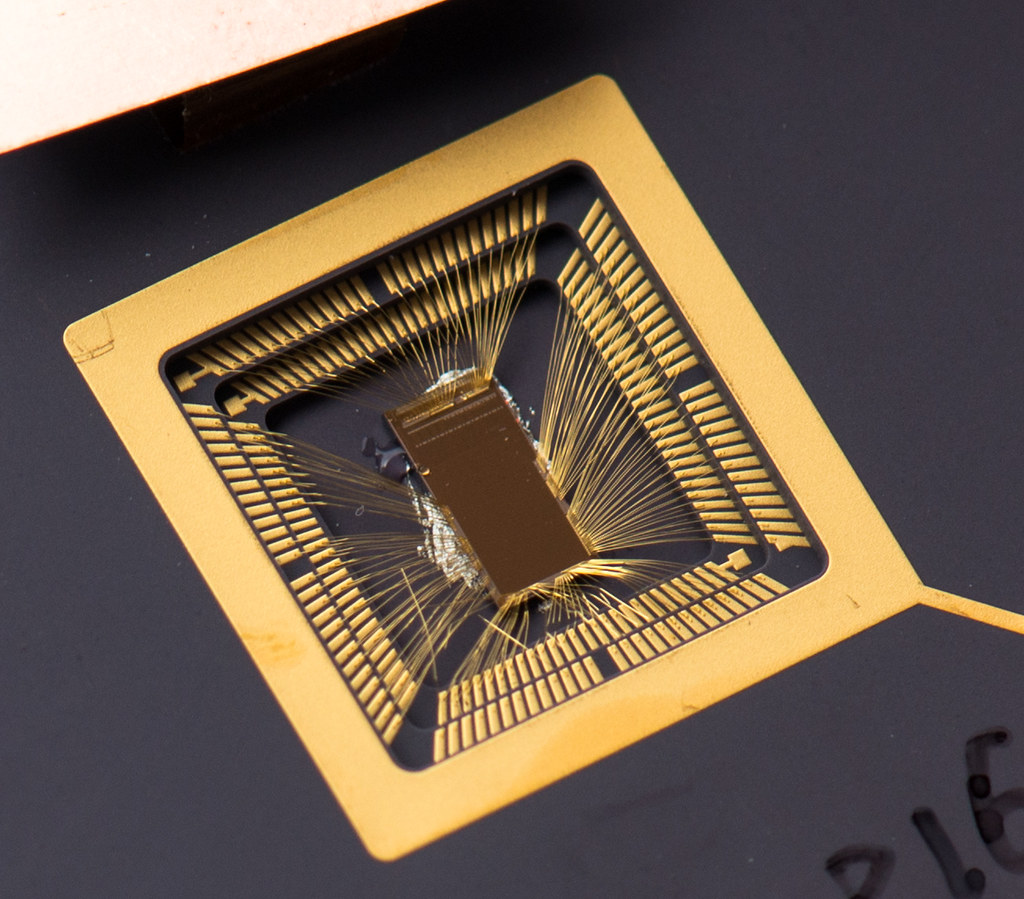

第一個基於RISC-V指令集的西班牙微處理器被稱為 蜥蜴,這是實現技術獨立的第一步。 然而,在這個項目的背後,有西班牙國家超級計算中心 BSC 協調的巨大努力和工作,以及 CSIC 和 UPC 的合作。

這個設計非常簡單,你的目標是進行第一次測試。 它是使用節點製造的 台積電 65nm,對於這個早期原型的相對簡單性來說足夠了,它在一些基準測試中進行了測試,看看它的能力,結果非常積極。 甚至比預期的還要好......

2019 年 XNUMX 月,該芯片的最終設計將發送至 EUROPRACTICE平台 之後,大約 100 份 Lagarto 副本將抵達巴塞羅那,開始進行測試,並作為同樣基於此 ISA 的 HPC 加速器的基礎。

德拉克

下一步是 德拉克 (為下一代計算機設計基於 RISC-V 的加速器)。 一種專為安全應用(例如硬件加密)以及科學應用(例如基因組分析、模擬加速或自動駕駛汽車領域)而設計的芯片。

當然,DRAC 也是由 BSC 主導,基於 開源RISC-V. 該項目預計將持續大約 3 年,其中多達 40 名研究人員將參與其中,並將由 UPC Ramón y Cajal 項目的研究員 Miquel Moretó 協調。 此外,融資約4萬歐元,一半來自ERDF基金,另一半來自該項目的合作夥伴。

這已經開始得到回報。 DVINO(按順序 DRAC 矢量) 它是源自該項目的第一代芯片。 顧名思義,它是一個有序的 IC,包括一個 Lagarto 內核以及一個專為分佈式計算設計的 Hydra 矢量處理器。

La 第二代 將芯片性能提高 15% 並添加新驅動器並將面積增加到 8.6 平方毫米。

處理器

處理器 是向前邁出的新一步,處理器版本計劃用於超級計算和服務器,以及用於車輛(例如:ADAS)、物聯網、移動設備等的高級駕駛員輔助系統。

BSC 再次參與了該項目。 它是第一個開源的歐洲全棧生態系統,其核心支柱將是基於 RISC-V 的 CPU,並具有 亂序執行的內核. 巴塞羅那中心將貢獻其在 HDL 中的 IP 核設計、仿真和必要工具方面的經驗。

與 BSC 一起,其他 歐洲層面的重要成員,如查爾姆斯理工大學、希臘研究與技術基金會、羅馬大學、Cortus、Christmann Informationstechnik、比勒費爾德大學、Extoll GmbH、Thales 和 Exapsys,以及 EuroHPC JU 的支持。

將開發和啟動硬件和軟件技術 在 FPGA 上進行測試 然後向ASICs致敬。 第一步將是設計一個高性能、高效率的 RISC-V 內核。 它將是具有連貫片外鏈接的單核和雙核,儘管稍後它們將從更複雜和更強大的設計開始。 還將設計基於 RISC-V 的矢量加速器,並探索生物信息學、人工智能、HPDA 等傳統超級計算工作負載。

eProcessor 也將 非常通用和靈活 在擴展它的時候,能夠添加更多的片上設備。

下一步:製造

這些芯片的設計將是歐洲的,而不是製造。 SiPearl 是 fabless,考慮到成員國在代工製造節點方面的落後,設計已經 委託台積電,它將採用 7nm 技術製造,並使用稱為 CoWoS(基板上芯片)的新型 3D 封裝技術。

然而,這個想法並不是要依賴外國工廠,所以歐盟也有 調動了很大一部分資金 資助舊大陸半導體製造的更新。 具體而言,它將撥款145.000億歐元,目標是在短期內達到2nm製造技術的節點。

這需要時間,並且旨在達到 2-3歲看過. 此外,台積電似乎正在合作使這成為可能,歐洲 ASML 也是半導體行業先進光刻機製造的領導者,總部位於荷蘭......

經濟事務和數字化轉型副總裁 Nadia Calviño 本人是這樣解釋的:«正在國家和國際層面開展工作,以 看看哪些西班牙和歐洲公司可以製造它們«, 參考這些芯片。 蒂埃里·布雷頓 (Thierry Breton) 在歐盟委員會的演講也是如此。 而且,用於該行業的資金將主要來自歐盟為數字化轉型和大流行後復蘇提供的援助。