यूरोप संयुक्त राज्य अमेरिका और चीन में डिजाइन और उत्पादित प्रौद्योगिकी पर बहुत अधिक निर्भर है। इसलिए, कुछ वर्षों से, कुछ चीजें यूरोपीय संघ के स्तर पर आगे बढ़ रही हैं ताकि ऐसा होना बंद हो जाए, और स्वतंत्रता है, विशेष रूप से कंप्यूटिंग में. EPI, eProcessor, SiPearl जैसी कंपनियां, साथ ही GAIA-X इन्फ्रास्ट्रक्चर जैसी परियोजनाएं इन आंदोलनों से उभरी हैं।

चूंकि अधिकांश आईएसए या आर्किटेक्चर यूरोप के बाहर स्वामित्व और स्वामित्व वाले हैं, खुला स्त्रोत इन परियोजनाओं के सफल होने के लिए यह महत्वपूर्ण रहा है। आईएसए आरआईएससी-वी इसने आशा लाई है, इन प्रोसेसरों और त्वरक को भू-राजनीतिक और भू-रणनीतिक युद्धों द्वारा बिना किसी प्रतिबंध या सीमा के उस पर निर्माण करने की अनुमति दी है।

ईपीआई (यूरोपीय प्रोसेसर पहल) का जन्म हुआ है

ईडीए (यूरोपीय रक्षा एजेंसी) सम्मेलन के बाद यूरोप की पहली प्रतिक्रियाओं में से एक, जहां सदस्य देशों की तकनीकी और औद्योगिक निर्भरता की समस्याओं का खुलासा किया गया था, एक संयुक्त पहल शुरू करना था जिसे कहा जाता है ईपीआई (यूरोपीय प्रोसेसर पहल). इसका उद्देश्य यूरोप में डिज़ाइन किए गए प्रोसेसर के लिए आवश्यक तंत्र को लागू करने के लिए एक संघ को एक साथ लाना है।

ये चिप्स, सिद्धांत रूप में, निजी उपयोग के लिए नहीं होंगे, लेकिन इन पर ध्यान केंद्रित किया जाएगा एचपीसी क्षेत्रयानी सुपरकंप्यूटिंग। ये उच्च-प्रदर्शन मशीनें विशेष रूप से महत्वपूर्ण हैं, और इस परियोजना के परिणामस्वरूप, यूरोपीय संघ के डेटा केंद्रों को 2023 से एक्सास्केल में पदोन्नत किया जाएगा। उनका ऑटोमोटिव और एयरोस्पेस उद्योगों जैसे अन्य क्षेत्रों में भी आवेदन होगा।

इसे संभव बनाने के लिए, RISC-V पर आधारित है त्वरक के लिए, जबकि जीपीपी या सामान्य प्रयोजन प्रोसेसर आईपी एआरएम कॉर्टेक्स नियोवर्स कोर पर आधारित होंगे, क्योंकि वे उन्हें डिजाइन प्रक्रिया को तेज करने की अनुमति देंगे और खरोंच से शुरू नहीं करेंगे।

ईपीआई भी है स्पेन सहित 26 विभिन्न यूरोपीय देशों के 10 भागीदार. परियोजना के केंद्रीय स्तंभों में से एक बार्सिलोना नेशनल सुपरकंप्यूटिंग सेंटर (बीसीएन) है। स्पेन स्वीडन से चल्मर्स टेक्निस्का होएगस्कोला एबी, जर्मनी से इंफिनियन टेक्नोलॉजीज, फ्रांस से सीईए, हॉलैंड में एसटीएमइक्रोइलेक्ट्रॉनिक्स, इटली में यूनिवर्सिटी डि बोलोग्ना, पुर्तगाल में लिस्बन के उच्च तकनीकी संस्थान, ग्रीस में फोर्थ, या ईटीएच जैसे भागीदारों से जुड़ गया है। स्विट्जरलैंड से प्रयोगशाला ज्यूरिख।

निजी कंपनी SiPearl, परियोजना को संचालित करने की क्षमता प्रदान करने के लिए बनाई गई है

संचालित करने के लिए, एक निजी कंपनी बनाई गई है जो इस ईपीआई परियोजना से उत्पन्न प्रौद्योगिकियों के प्रबंधन के लिए जिम्मेदार होगी। उसका नाम है सी पर्ल और इसका मुख्यालय फ्रांस में है। इसके अलावा, उन्होंने जर्मनी में और एक अन्य स्पेन में, विशेष रूप से बार्सिलोना में, अपने बीएससी भागीदारों के करीब होने के लिए एक सहायक कंपनी खोली है।

यह स्टार्टअप के सार्वजनिक बजट से शुरू हुआ यूरो के 80 लाखों, जो उन सभी खर्चों को कवर करने के लिए पर्याप्त नहीं हैं जो इतनी गहराई की परियोजना का तात्पर्य है। इसलिए, SiPerl निजी तौर पर, मुख्य रूप से शेयरों से 100 मिलियन यूरो से अधिक जुटाने का प्रभारी होगा।

इसके सह-संस्थापक और सीईओ, फिलिप नोटन, सिलिकॉन वैली से लाए गए कुछ डिजाइनरों के साथ-साथ परियोजना को सभी गारंटी देने के अनुभव के साथ सही कर्मचारियों की भर्ती के लिए एक शानदार काम कर रहा है। वे तकनीकी साझेदारों की भी तलाश कर रहे हैं, जैसे कि ग्राफकोर, एक प्रमुख ब्रिटिश कंपनी, कृत्रिम बुद्धिमत्ता के साथ चिप्स को तेज करने के मामले में जो एचपीसी में बहुत महत्वपूर्ण हैं।

बीएससी एक प्रमुख भागीदार: लैगार्टो चिप से ड्रेक तक

El बीएससी (बार्सिलोना सुपरकंप्यूटिंग सेंटर) यह इस परियोजना का एक महत्वपूर्ण हिस्सा है। न केवल वे इन प्रोसेसर के डिजाइन और विकास में योगदान दे रहे हैं, बल्कि मारेनोस्ट्रम 5 पहले से ही इस परियोजना के फल का परीक्षण शुरू कर देगा ...

छिपकली

RISC-V निर्देश सेट पर आधारित पहले स्पेनिश माइक्रोप्रोसेसर को डब किया गया है छिपकली, और यह तकनीकी स्वतंत्रता तक पहुंचने का पहला कदम है। हालांकि, इस परियोजना के पीछे स्पेन के राष्ट्रीय सुपरकंप्यूटिंग केंद्र के बीएससी द्वारा समन्वित एक महान प्रयास और कार्य है, साथ ही सीएसआईसी और यूपीसी का सहयोग भी है।

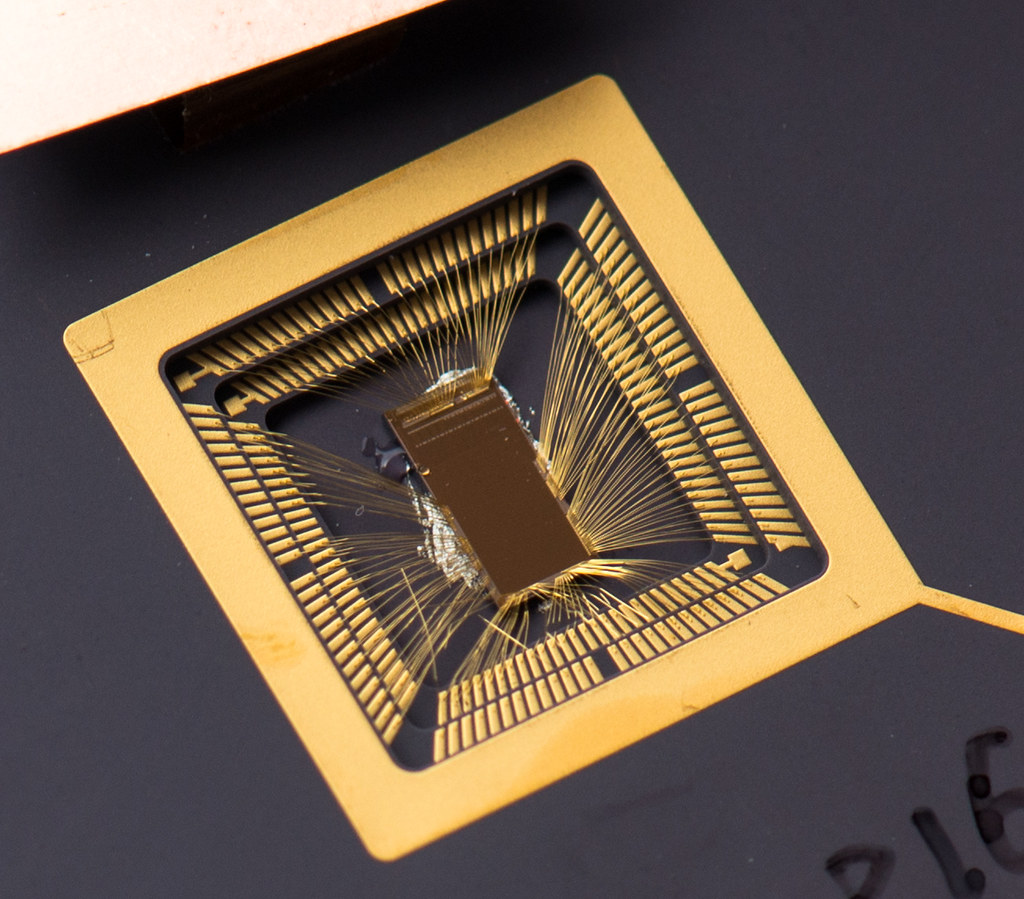

यह डिज़ाइन बहुत सरल है, और आपका लक्ष्य पहले परीक्षण करना है। यह के नोड का उपयोग करके निर्मित किया गया था TSMC पर 65nm, इस प्रारंभिक प्रोटोटाइप की सापेक्ष सादगी के लिए पर्याप्त है कि यह देखने के लिए कुछ बेंचमार्क में इसका परीक्षण किया गया था कि यह क्या करने में सक्षम था, और परिणाम काफी सकारात्मक थे। उम्मीद से भी बेहतर...

मई 2019 में इस चिप का अंतिम डिज़ाइन को भेजा जाएगा EUROPRACTICE मंच ईसी की, और उसके बाद लैगार्टो की लगभग 100 प्रतियां परीक्षण के साथ शुरू करने और एचपीसी के लिए त्वरक के लिए आधार के रूप में काम करने के लिए बार्सिलोना पहुंचेंगी जो इस आईएसए पर भी आधारित है।

डीआरएसी

अगला कदम था डीआरएसी (अगली पीढ़ी के कंप्यूटरों के लिए आरआईएससी-वी-बीएसईडी एक्सेलेरेटर डिजाइन करना)। सुरक्षा अनुप्रयोगों के लिए डिज़ाइन की गई एक चिप, जैसे हार्डवेयर एन्क्रिप्शन, साथ ही वैज्ञानिक अनुप्रयोग जैसे जीनोम विश्लेषण, सिमुलेशन त्वरण, या स्वायत्त वाहन क्षेत्र।

बेशक, DRAC का नेतृत्व BSC भी करता है और यह किसकी वास्तुकला पर आधारित है? खुला स्रोत आरआईएससी-वी. यह परियोजना लगभग 3 वर्षों तक चलने की उम्मीद है, जिसमें 40 शोधकर्ता भाग लेंगे और यूपीसी में रामोन वाई काजल कार्यक्रम के शोधकर्ता मिकेल मोरेटो द्वारा समन्वयित किया जाएगा। इसके अलावा, वित्त पोषण लगभग 4 मिलियन यूरो है, आधा ईआरडीएफ फंड से और दूसरा आधा इस परियोजना के भागीदारों से।

इसका भुगतान पहले ही शुरू हो चुका है। DVINO (DRAC वेक्टर इन-ऑर्डर) यह इस परियोजना और पहली पीढ़ी से प्राप्त एक चिप है। जैसा कि इसके नाम से पता चलता है, यह एक सुव्यवस्थित आईसी है जिसमें वितरित कंप्यूटिंग के लिए डिज़ाइन किया गया हाइड्रा वेक्टर प्रोसेसर के साथ लैगार्टो कोर शामिल है।

La दूसरी पीढी चिप प्रदर्शन में 15% तक सुधार करें और नए ड्राइवर जोड़ें और क्षेत्र को 8.6 वर्ग मिलीमीटर तक बढ़ाएं।

ई-प्रोसेसर

ई-प्रोसेसर नया कदम आगे है, सुपरकंप्यूटिंग और सर्वर के लिए नियोजित संस्करणों के साथ एक प्रोसेसर, साथ ही वाहनों के लिए उन्नत ड्राइवर सहायता प्रणाली (जैसे: ADAS), IoT, मोबाइल डिवाइस, आदि।

फिर से बीएससी इस परियोजना में शामिल है। यह पहला खुला स्रोत यूरोपीय पूर्ण-स्टैक पारिस्थितिकी तंत्र है और जिसका केंद्रीय स्तंभ आरआईएससी-वी पर आधारित सीपीयू होगा और एक के साथ आउट-ऑफ-ऑर्डर निष्पादन के साथ कर्नेल. बार्सिलोना केंद्र एचडीएल, अनुकरण और आवश्यक उपकरणों में आईपी कोर के डिजाइन में अपने अनुभव का योगदान देगा।

बीएससी के साथ अन्य यूरोपीय स्तर पर महत्वपूर्ण सदस्य, जैसे चल्मर्स यूनिवर्सिटी ऑफ़ टेक्नोलॉजी, फ़ाउंडेशन फ़ॉर रिसर्च एंड टेक्नोलॉजी हेलस, यूनिवर्सिटा डिगली स्टडी डि रोमा ला सैपिएन्ज़ा, कॉर्टस, क्रिस्टमैन इंफॉर्मेशनटेक्निक, यूनिवर्सिटैट बीलेफेल्ड, एक्सटोल जीएमबीएच, थेल्स और एक्सैप्सिस, साथ ही यूरोएचपीसी जेयू का समर्थन।

हार्डवेयर और सॉफ्टवेयर प्रौद्योगिकियों को विकसित और शुरू किया जाएगा FPGAs पर परीक्षण फिर ASICs को सलाम देने के लिए। पहला कदम एक उच्च-प्रदर्शन, उच्च-दक्षता वाले RISC-V कोर को डिजाइन करना होगा। यह सुसंगत ऑफ-चिप लिंक के साथ सिंगल-कोर और डुअल-कोर होगा, हालांकि बाद में वे अधिक जटिल और शक्तिशाली डिजाइनों के साथ शुरू होंगे। आरआईएससी-वी-आधारित वेक्टर त्वरक को भी डिजाइन किया जाएगा और पारंपरिक सुपरकंप्यूटिंग वर्कलोड जैसे जैव सूचना विज्ञान, एआई, एचपीडीए, आदि का पता लगाया जाएगा।

ई-प्रोसेसर भी होगा बहुत बहुमुखी और लचीला स्केलिंग के समय, अधिक ऑन-चिप डिवाइस जोड़ने में सक्षम होने के लिए।

अगला कदम: निर्माण

इन चिप्स का डिजाइन यूरोपियन होगा, जो नहीं होगा वह है मैन्युफैक्चरिंग। SiPearl एक दंतकथा है, और सदस्य देशों में फाउंड्री निर्माण नोड्स के बैकलॉग को देखते हुए, डिजाइन किया गया है TSMC . को कमीशन किया गया, जो इसे 7nm तकनीक में निर्मित करेगा और CoWoS (चिप-ऑन-वेफर-ऑन-सब्सट्रेट) नामक नई 3D पैकेजिंग तकनीक का उपयोग करेगा।

हालाँकि, विचार उसके लिए विदेशी कारखानों पर निर्भर नहीं होना है, इसलिए यूरोपीय संघ ने भी पैसे का एक बड़ा हिस्सा जुटाया पुराने महाद्वीप में अर्धचालक निर्माण के अद्यतन को वित्तपोषित करने के लिए। विशेष रूप से, यह अल्पावधि में 145.000nm विनिर्माण प्रौद्योगिकी के साथ एक नोड तक पहुंचने के उद्देश्य से 2 मिलियन यूरो आवंटित करेगा।

इसमें समय लगता है, और पहुंचने का इरादा है 2-3 साल देखा years. इसके अलावा, ऐसा लगता है कि TSMC इसे संभव बनाने के लिए सहयोग कर रहा है, और यूरोपीय ASML भी, जो सेमीकंडक्टर उद्योग के लिए उन्नत फोटोलिथोग्राफी मशीनों के निर्माण में अग्रणी है, और जो नीदरलैंड में स्थित है ...

आर्थिक मामलों और डिजिटल परिवर्तन के उपाध्यक्ष नादिया कैल्विनो ने इसे इस तरह समझाया है: «इसके लिए राष्ट्रीय और अंतरराष्ट्रीय स्तर पर काम किया जा रहा है देखें कि कौन सी स्पेनिश और यूरोपीय कंपनियां उनका निर्माण कर सकती हैं«, इन चिप्स के संदर्भ में। उसी नस में यूरोपीय आयोग में थियरी ब्रेटन का भाषण था। और यह है कि इस क्षेत्र के लिए नियत धन यूरोपीय संघ द्वारा डिजिटल परिवर्तन और महामारी के बाद की वसूली के लिए प्रदान की गई सहायता से काफी हद तक आएगा।