Eropah sangat bergantung pada teknologi yang direka dan dihasilkan di Amerika Syarikat dan China. Itulah sebabnya, selama beberapa tahun, beberapa perkara telah bergerak di peringkat EU sehingga ini tidak lagi berlaku mempunyai kebebasan, terutamanya dalam pengkomputeran. Projek seperti EPI, eProcessor, syarikat seperti SiPearl, dan juga infrastruktur GAIA-X telah muncul dari pergerakan ini.

Oleh kerana kebanyakan ISA atau seni bina adalah milik dan dimiliki di luar Eropah, sumber terbuka Projek-projek ini berjaya. The ISA RISC-V ini telah membawa harapan, yang memungkinkan pemproses dan pemecut ini terus membangun tanpa halangan atau batasan oleh perang geopolitik dan geostrategik.

EPI (Inisiatif Pemproses Eropah) dilahirkan

Salah satu reaksi pertama Eropah, selepas persidangan EDA (European Defense Agency) di mana masalah ketergantungan teknologi dan industri dari negara-negara anggota terdedah, adalah dengan memulakan inisiatif bersama yang disebut EPI (Inisiatif Pemproses Eropah). Objektifnya adalah untuk mengumpulkan sebuah konsortium untuk melaksanakan mekanisme yang diperlukan untuk merancang prosesor di Eropah.

Cip ini, pada prinsipnya, bukan untuk kegunaan peribadi, tetapi akan diberi tumpuan sektor HPC, iaitu superkomputer. Mesin berprestasi tinggi ini sangat kritikal, dan sebagai hasil projek ini, pusat data EU akan dipromosikan ke Exascale mulai tahun 2023. Mereka juga akan mempunyai aplikasi di sektor lain seperti industri automotif dan aeroangkasa.

Untuk menjadikannya mungkin, berdasarkan RISC-V untuk pemecut, sementara GPP atau pemproses tujuan umum akan didasarkan pada inti IP ARM Cortex Neoverse, kerana ia akan memungkinkan mereka mempercepat proses reka bentuk dan tidak bermula dari awal.

EPI juga mempunyai 26 rakan dari 10 negara Eropah yang berbeza, termasuk Sepanyol. Salah satu tonggak utama projek ini ialah Pusat Superkomputeran Nasional Barcelona (BCN). Sepanyol disertai oleh rakan-rakan seperti Chalmers Tekniska Hoegskola AB dari Sweden, Infineon Technologies dari Jerman, CEA dari Perancis, STMicroelectronics di Holland, Università di Bologna di Itali, Institut Teknikal Tinggi Lisbon di Portugal, FORTH di Yunani, atau ETH makmal Zürich dari Switzerland.

SiPearl, syarikat swasta, diciptakan untuk menyediakan projek dengan kemampuan untuk beroperasi

Untuk beroperasi, sebuah syarikat swasta telah diwujudkan yang akan bertanggungjawab menguruskan teknologi yang dihasilkan dari projek EPI ini. Nama dia ialah YesPearl dan ibu pejabatnya berada di Perancis. Di samping itu, mereka telah membuka anak syarikat di Jerman dan satu lagi di Sepanyol, khususnya di Barcelona, untuk dekat dengan rakan BSC mereka.

Permulaan ini dimulakan dengan anggaran awam sebanyak 80 juta euro, yang tidak mencukupi untuk menampung semua perbelanjaan yang disiratkan oleh projek sedalam itu. Oleh itu, SiPearl juga akan bertanggungjawab untuk mengumpulkan lebih dari 100 juta euro secara peribadi, terutamanya dari saham.

Pengasas bersama dan Ketua Pegawai Eksekutifnya, Philippe Notton, melakukan pekerjaan yang hebat untuk merekrut beberapa pereka yang dibawa dari Silicon Valley, serta kakitangan yang tepat dengan pengalaman untuk memberikan semua projek jaminan. Mereka juga mencari rakan kongsi teknologi, seperti Graphcore, sebuah syarikat Britain terkemuka dari segi mempercepat cip dengan kepintaran buatan yang sangat penting dalam HPC.

BSC rakan kongsi utama: Dari cip Lagarto hingga Drac

El BSC (Pusat Superkomputer Barcelona) ia adalah kunci utama projek ini. Mereka bukan sahaja menyumbang kepada reka bentuk dan pengembangan pemproses ini, tetapi Marenostrum 5 akan mula menguji hasil projek ini ...

Kadal

Mikroprosesor Sepanyol pertama berdasarkan set arahan RISC-V telah dijuluki Kadal, dan ini adalah langkah pertama untuk mencapai kebebasan teknologi. Namun, di sebalik projek ini ada usaha dan kerja keras yang dikoordinasikan oleh BSC National Supercomputing Center of Spain, serta kolaborasi CSIC, dan UPC.

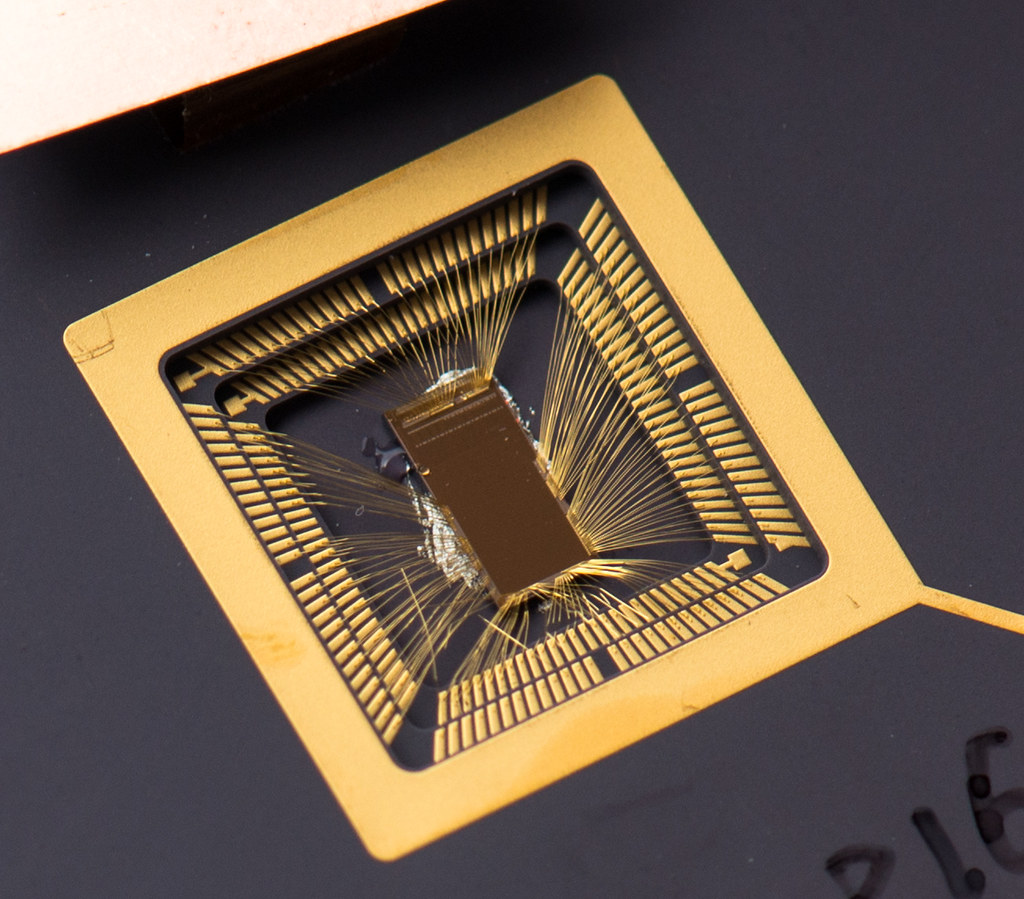

Reka bentuk ini sangat mudah, dan objektif anda adalah untuk menjalankan ujian pertama. Ia dihasilkan menggunakan nod 65nm di TSMC, cukup untuk kesederhanaan relatif prototaip awal ini bahawa ia diuji dalam beberapa penanda aras untuk melihat kemampuannya, dan hasilnya cukup positif. Lebih baik dari yang dijangkakan ...

Pada bulan Mei 2019, reka bentuk akhir cip ini akan dihantar ke Platform EUROPRACTICE EC, dan selepas itu kira-kira 100 salinan Lagarto akan tiba di Barcelona untuk memulakan ujian dan berfungsi sebagai pangkalan bagi pemecut untuk HPC yang juga berdasarkan ISA ini.

DRAC

Langkah seterusnya adalah DRAC (Merancang RISC-V-bsed Accelerators untuk Komputer generasi akan datang). Cip yang direka untuk aplikasi keselamatan, seperti enkripsi perkakasan, serta aplikasi saintifik seperti analisis genom, percepatan simulasi, atau sektor kenderaan autonomi.

Sudah tentu, DRAC juga diterajui oleh BSC dan berdasarkan seni bina sumber terbuka RISC-V. Projek ini dijangka berlangsung sekitar 3 tahun, di mana sehingga 40 penyelidik akan mengambil bahagian dan akan dikoordinasikan oleh Miquel Moretó, seorang penyelidik dari program Ramón y Cajal di UPC. Di samping itu, pembiayaan bernilai kira-kira 4 juta euro, separuh dari dana ERDF dan separuh lagi dari rakan kongsi projek ini.

Ini sudah mula membuahkan hasil. DVINO (DRAC Vektor DALAM Pesanan) Ia adalah cip yang berasal dari projek ini dan generasi pertama. Seperti namanya, IC adalah teratur yang merangkumi teras Lagarto dan pemproses vektor Hydra yang direka untuk pengkomputeran diedarkan.

La generasi kedua meningkatkan prestasi cip sebanyak 15% dan menambah pemacu baru dan meningkatkan luasnya menjadi 8.6 milimeter persegi.

eProsesor

eProsesor adalah langkah baru ke depan, pemproses dengan versi yang dirancang untuk superkomputer dan pelayan, serta sistem bantuan pemandu canggih untuk kenderaan (mis.: ADAS), IoT, peranti mudah alih, dll.

Sekali lagi BSC adalah orang yang terlibat dalam projek ini. Ia adalah ekosistem tumpukan penuh Eropah sumber terbuka pertama dan yang menjadi tonggak utamanya akan menjadi CPU berdasarkan RISC-V dan dengan kernel dengan pelaksanaan di luar pesanan. Pusat Barcelona akan menyumbangkan pengalamannya dalam reka bentuk inti IP dalam HDL, emulasi, dan alat yang diperlukan.

Bersama dengan BSC, lain-lain anggota penting di peringkat Eropahseperti Universiti Teknologi Chalmers, Yayasan Penyelidikan dan Teknologi Hellas, Universita degli Studi di Roma La Sapienza, Cortus, Christmann Informationstechnik, Universität Bielefeld, Extoll GmbH, Thales dan Exapsys, serta sokongan EuroHPC JU.

Teknologi perkakasan dan perisian akan dikembangkan dan dimulakan ujian pada FPGA kemudian memberi selawat kepada ASIC. Langkah pertama ialah merancang teras RISC-V berprestasi tinggi dan berprestasi tinggi. Ia akan menjadi satu-teras dan dua-teras dengan pautan off-chip yang koheren, walaupun kemudian mereka akan bermula dengan reka bentuk yang lebih kompleks dan kuat. Pemecut vektor berasaskan RISC-V juga akan dirancang dan beban kerja superkomputer tradisional seperti bioinformatik, AI, HPDA, dan lain-lain akan diterokai.

EProcessor juga akan sangat serba boleh dan fleksibel pada masa penskalaannya, untuk dapat menambahkan lebih banyak peranti on-chip.

Langkah seterusnya: pembuatan

Reka bentuk kerepek ini akan menjadi Eropah, yang tidak akan dibuat ialah pembuatannya. SiPearl adalah fabless, dan mengingat node pembuatan faundri di negara anggota, reka bentuknya telah ditugaskan ke TSMC, yang akan menghasilkannya dalam teknologi 7nm dan menggunakan teknologi pembungkusan 3D baru yang disebut CoWoS (Chip-on-Wafer-on-Substrate).

Walau bagaimanapun, ideanya tidak bergantung pada kilang asing untuk itu, jadi EU juga menggerakkan sebahagian besar wang untuk membiayai pengemaskinian pembuatan semikonduktor di Benua Lama. Secara khusus, ia akan memperuntukkan 145.000 juta euro, dengan tujuan mencapai node dengan teknologi pembuatan 2nm dalam jangka pendek.

Ini memerlukan masa, dan bertujuan untuk dicapai 2-3 tahun dilihat. Selain itu, nampaknya TSMC bekerjasama untuk mewujudkannya, dan juga ASML Eropah, yang merupakan peneraju pembuatan mesin fotolitografi canggih untuk industri semikonduktor, dan berpusat di Belanda ...

Nadia Calviño sendiri, Naib Presiden Hal Ehwal Ekonomi dan Transformasi Digital telah menjelaskannya seperti ini:Kerja sedang dilakukan di peringkat nasional dan antarabangsa untuk lihat syarikat Sepanyol dan Eropah mana yang boleh mengeluarkannya«, Merujuk kepada kerepek ini. Dalam nada yang sama adalah ucapan Thierry Breton di Suruhanjaya Eropah. Dan dana yang ditujukan untuk sektor ini sebahagian besarnya akan datang dari bantuan yang diberikan oleh EU untuk transformasi digital dan pemulihan pasca wabak.