A Europa é fortemente dependente de tecnologia projetada e produzida nos Estados Unidos e na China. Por esta razão, nos últimos anos, algumas coisas têm se movido a nível da UE para que isso deixe de ser o caso, e para ter independência, principalmente na área de informática. Projetos como EPI, eProcessor, empresas como SiPearl, bem como a infraestrutura GAIA-X surgiram desses movimentos.

Uma vez que a maioria das ISAs ou arquiteturas são proprietárias e de propriedade fora da Europa, Código aberto Tem sido a chave para o sucesso desses projetos. O ISA RISC-V trouxe esperança, permitindo que esses processadores e aceleradores construíssem sobre ele sem qualquer restrição ou limitação por guerras geopolíticas e geoestratégicas.

Nasce a EPI (European Processor Initiative)

Uma das primeiras reacções da Europa, após a conferência da EDA (Agência Europeia de Defesa) onde foram expostos os problemas de dependência tecnológica e industrial dos países membros, foi o lançamento de uma iniciativa conjunta denominada EPI (Iniciativa do Processador Europeu). Seu objetivo é reunir um consórcio para implementar os mecanismos necessários para que os processadores sejam projetados na Europa.

Esses chips, em princípio, não serão para uso privado, mas terão como foco o setor de HPC, isto é, supercomputação. Essas máquinas de alto desempenho são especialmente críticas e, como resultado deste projeto, os data centers da UE serão promovidos a Exascale a partir de 2023. Eles também terão aplicação em outros setores, como as indústrias automotiva e aeroespacial.

Para tornar isso possível, baseado em RISC-V para aceleradores, enquanto os GPPs ou processadores de uso geral serão baseados em núcleos IP ARM Cortex Neoverse, pois eles permitirão acelerar o processo de design e não começar do zero.

EPI também tem 26 parceiros de 10 países europeus diferentes, incluindo Espanha. Um dos pilares centrais do projeto é o Centro Nacional de Supercomputação de Barcelona (BCN). A Espanha é acompanhada por parceiros como Chalmers Tekniska Hoegskola AB da Suécia, Infineon Technologies da Alemanha, CEA da França, STMicroelectronics na Holanda, a Università di Bologna na Itália, o Instituto Superior Técnico de Lisboa em Portugal, FORTH na Grécia ou o ETH laboratório Zürich da Suíça.

SiPearl, a empresa privada, é criada para dotar o projeto com a capacidade de operar

Para operar, foi criada uma empresa privada que se encarregará de gerir as tecnologias resultantes deste projeto de EPI. Seu nome é SiPearlGenericName e sua sede está na França. Além disso, abriram uma filial na Alemanha e outra na Espanha, especificamente em Barcelona, para estarem próximos de seus parceiros do BSC.

Esta startup começou com um orçamento público de 80 milhões de euros, que não são suficientes para cobrir todas as despesas que um projeto de tamanha profundidade acarreta. Portanto, o SiPearl também será responsável por captar mais de 100 milhões de euros de forma privada, principalmente com ações.

Seu cofundador e CEO, Philippe Notton, está fazendo um trabalho fantástico ao recrutar alguns designers trazidos do Vale do Silício, bem como a equipe certa com experiência para dar todas as garantias ao projeto. Também procuram parceiros tecnológicos, como a Graphcore, empresa britânica líder em chips de aceleração com inteligência artificial, tão importantes em HPC.

BSC um parceiro-chave: do chip Lagarto ao Drac

El BSC (Centro de Supercomputação de Barcelona) é uma peça fundamental deste projeto. Eles não estão apenas contribuindo para o design e desenvolvimento desses processadores, mas o Marenostrum 5 já começará a testar os frutos desse projeto ...

Lagarto

O primeiro microprocessador espanhol baseado no conjunto de instruções RISC-V foi apelidado Lagarto, e é o primeiro passo para alcançar a independência tecnológica. No entanto, por trás deste projeto existe um grande esforço e trabalho coordenado pelo BSC do Centro Nacional de Supercomputação da Espanha, bem como a colaboração do CSIC e da UPC.

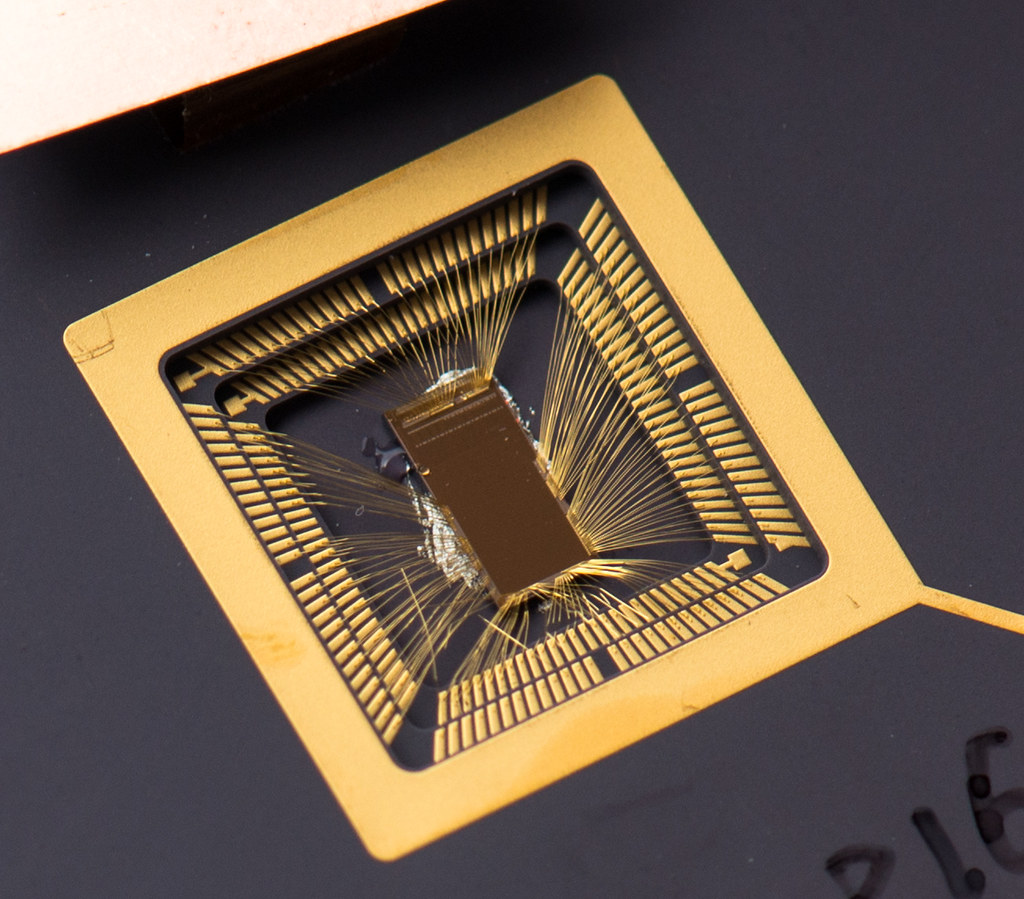

Este desenho é muito simples e seu objetivo é realizar os primeiros testes. Foi fabricado usando um nó 65nm em TSMC, o suficiente para a relativa simplicidade deste protótipo inicial que foi testado em alguns benchmarks para ver do que era capaz, e os resultados foram bastante positivos. Ainda melhor do que o esperado ...

Em maio de 2019, o design final deste chip seria enviado para o Plataforma EUROPRACTICE da CE, e depois disso chegariam a Barcelona cerca de 100 exemplares do Lagarto para iniciar os testes e servir de base para o acelerador do HPC que também está baseado neste ISA.

DRAC

O próximo passo foi DRAC (Projetando aceleradores RISC-V-bsed para a próxima geração de computadores). Um chip projetado para aplicações de segurança, como criptografia de hardware, bem como aplicações científicas, como análise de genoma, aceleração de simulação ou setor de veículos autônomos.

Claro, o DRAC também é liderado pelo BSC e é baseado na arquitetura de RISC-V de código aberto. O projeto está previsto para durar cerca de 3 anos, no qual participarão até 40 pesquisadores e será coordenado por Miquel Moretó, pesquisador do programa Ramón y Cajal da UPC. Além disso, o financiamento foi de cerca de 4 milhões de euros, metade proveniente de fundos FEDER e a outra metade de parceiros deste projecto.

Isso já começou a dar frutos. DVINO (vetor DRAC em ordem) É um chip derivado deste projeto e de primeira geração. Como o próprio nome sugere, é um IC bem ordenado que inclui um núcleo Lagarto junto com um processador vetorial Hydra projetado para computação distribuída.

La segunda geração melhore o desempenho do chip em 15% e adicione novos drivers e aumente a área para 8.6 milímetros quadrados.

eProcessador

eProcessador é o novo passo em frente, um processador com versões planejadas para supercomputação e servidores, além de sistemas avançados de assistência ao motorista para veículos (ex: ADAS), IoT, dispositivos móveis, etc.

Mais uma vez, o BSC é quem está envolvido neste projeto. É o primeiro ecossistema de pilha completo europeu de código aberto e cujo pilar central será uma CPU baseada em RISC-V e com um kernel com execução fora de ordem. O centro de Barcelona contribuirá com sua experiência no projeto de núcleos IP em HDL, emulação e nas ferramentas necessárias.

Junto com o BSC, outros membros importantes a nível europeu, como a Chalmers University of Technology, a Fundação para Pesquisa e Tecnologia Hellas, a Universita degli Studi di Roma La Sapienza, a Cortus, a Christmann Informationstechnik, a Universität Bielefeld, a Extoll GmbH, a Thales e a Exapsys, bem como o apoio da EuroHPC JU.

As tecnologias de hardware e software serão desenvolvidas e iniciadas teste em FPGAs para então dar o salat aos ASICs. A primeira etapa será projetar um núcleo RISC-V de alto desempenho e alta eficiência. Será um single-core e um dual-core com link off-chip coerente, embora mais tarde eles comecem com designs mais complexos e poderosos. O acelerador vetorial baseado em RISC-V também será projetado e cargas de trabalho de supercomputação tradicionais, como bioinformática, IA, HPDA, etc. serão exploradas.

O eProcessor também será muito versátil e flexível no momento de dimensioná-lo, para poder adicionar mais dispositivos no chip.

A próxima etapa: fabricação

O design desses chips será europeu, o que não será é a fabricação. SiPearl é um fabless, e dada a carteira de nós de fabricação de fundição nos países membros, o projeto foi encomendado a TSMC, que o fabricará em tecnologia de 7 nm e usando a nova tecnologia de embalagem 3D chamada CoWoS (Chip-on-Wafer-on-Substrate).

No entanto, a ideia é não depender de fábricas estrangeiras para isso, então a UE também tem mobilizou grande parte do dinheiro para financiar a atualização da fabricação de semicondutores no Velho Continente. Especificamente, irá alocar 145.000 milhões de euros, com o objetivo de atingir, a curto prazo, um nó com tecnologia de fabricação de 2nm.

Isso leva tempo e tem como objetivo alcançar 2-3 anos vistos. Além disso, parece que a TSMC está colaborando para tornar isso possível, e também a ASML europeia, que é líder na fabricação de máquinas de fotolitografia avançada para a indústria de semicondutores e tem sede na Holanda ...

A própria Nadia Calviño, Vice-presidente de Assuntos Econômicos e Transformação Digital explicou assim: «O trabalho está sendo feito em nível nacional e internacional para veja quais empresas espanholas e europeias podem fabricá-los«, Em referência a esses chips. Na mesma linha foi o discurso de Thierry Breton na Comissão Europeia. E é que os fundos destinados ao setor virão em grande parte da ajuda prestada pela UE à transformação digital e à recuperação pós-pandémica.