Las FPGAs han pasado de ser curiosidades para prototipado a convertirse en piezas clave de cómputo en centros de datos, sistemas embebidos y soluciones de alto rendimiento. Su propuesta es única: lógica digital que puedes reconfigurar cuantas veces quieras, combinando la flexibilidad del software con la velocidad del hardware especializado.

Si alguna vez te has peleado con un Arduino y un puñado de cables, imagina una protoboard del tamaño de una pista de baloncesto, sin jumpers y conectada de forma virtual. Eso es, a lo bestia, lo que te ofrece una FPGA: un lienzo programable de bloques lógicos, memoria y rutas de interconexión sobre el que dibujar desde contadores sencillos hasta procesadores completos.

De los PLD a las FPGAs: una línea temporal que lo cambió todo

La historia arranca en 1984, cuando Ross Freeman, Bernard Vonderschmitt y James V. Barnett II fundan Xilinx en pleno auge de la microelectrónica. Su idea cristaliza en 1985 con la XC2064, la primera FPGA comercial, que toma el relevo de los PLD (PROM, PAL y derivados) con un enfoque mucho más granular y reconfigurable. En paralelo, el mundo ASIC seguía con celdas estándar y propuestas como la ULA de Ferranti, pero faltaba un puente verdaderamente flexible entre el diseño lógico y el silicio.

Aquellas primeras FPGAs de Xilinx se basaban en la arquitectura Logic Cell Array (LCA): bloques de entrada/salida (IOB), bloques lógicos y una matriz de interconexión programable. Con esa tríada, un diseñador podía definir pines, construir funciones lógicas y cablearlas de forma virtual, como si fuese una protoboard sin cables. Esa visión dio paso a familias como las XC 2000, y a una evolución fulgurante en densidad y prestaciones.

Las cifras ilustran el salto: 8.192 puertas en 1982 (Burroughs Advanced Systems Group), 9.000 en 1987 (Xilinx), 600.000 en 1992 (Naval Surface Warfare Department) y millones a principios de los 2000. El mercado acompañó: de 14 millones de dólares en 1987 a 385 millones en 1993, 1.900 millones en 2005, cerca de 2.750 millones en 2010, 5.400 millones en 2013 y en torno a 9.800 millones en 2020. La demanda se disparó conforme las FPGAs demostraron ser útiles y rentables fuera del puro prototipado.

En cuanto a configuración, los primeros dispositivos cargaban su bitstream desde EPROM/EEPROM/ROM o desde un PC por puerto serie al encender. Al ser tecnología basada en SRAM, el contenido se pierde sin alimentación, así que hay que reconfigurar en cada arranque. Hoy es habitual cargar desde memoria flash (por ejemplo, vía tarjeta SD) y programar por USB o JTAG, manteniendo el mismo principio: un flujo de configuración que define lógica e interconexiones de forma determinista y repetible.

Arquitectura y funcionamiento: piezas, flujo y reconfiguración

En esencia, una FPGA es una cuadrícula de bloques lógicos (LUTs, biestables, rutas de carry, etc.), bloques de memoria (BRAM), recursos de DSP y entradas/salidas, todo ello unido por una red de interconexiones jerárquica. Con esa base, implementas desde puertas básicas (AND, OR, XOR) y flip-flops tipo D hasta sumadores, multiplicadores o pipelines complejos, todo enlazado con un enrutado programable que actúa como el “cableado virtual” de tu diseño.

La configuración se vuelca como un bitstream que define tanto la función de cada LUT como el estado de los multiplexores de interconexión. La mayoría de dispositivos modernos son volátiles (RAM) y necesitan recarga, aunque existen opciones no volátiles (flash, fusibles y antifusibles), reprogramables o de única programación. Las variantes reprogramables suelen admitir en torno a 10.000 ciclos de escritura/borrado.

Un rasgo diferenciador es la reconfiguración parcial: puedes reprogramar una región mientras el resto del sistema sigue funcionando. Esto habilita escenarios de computación reconfigurable, swaps de aceleradores en caliente o actualizaciones dinámicas sin parar el dispositivo. En paralelo, muchas FPGAs integran funciones de alto nivel directamente en la matriz (multiplicadores de alto rendimiento, bloques de DSP, RAM dual-port) y, cada vez más, periféricos de propósito específico.

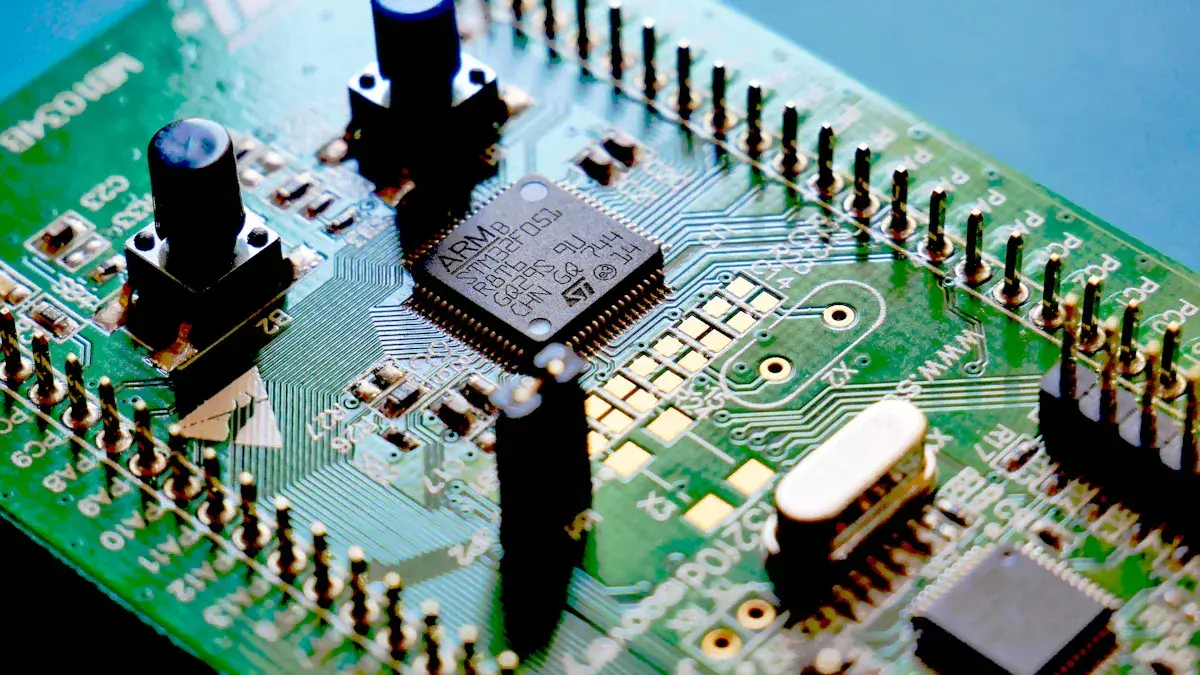

Ese camino llevó a los “sistemas programables en chip”: Virtex-II Pro y Virtex-4 integraron núcleos PowerPC con la lógica programable; Atmel FPSLIC combinó un AVR con FPGA; y, más adelante, Xilinx Zynq fusionó CPUs Arm con lógica reconfigurable. En el lado “blando”, los núcleos MicroBlaze y PicoBlaze (Xilinx), Nios/Nios II (Altera), o LatticeMicro32 y LatticeMicro8 (Lattice) permiten instanciar procesadores como IP dentro de la FPGA para construir SoCs a medida y explorar plataformas RISC‑V como potencia RISC‑V en un mini módulo.

De “cables y C” a hardware virtual: comparación con microcontroladores

Quien viene del mundo Arduino suele montar el circuito en protoboard, programar en C y conectar con jumpers. Con FPGAs, la dinámica cambia: describes el hardware en un HDL y el “cableado” lo decide el enrutador, sin lío de cables. Si lo piensas como una placa infinita sin limitaciones físicas, estás muy cerca de la realidad: incluso puedes “colocar” distintos procesadores y periféricos en el diseño según te convenga. En la práctica, es como disponer de una plataforma modular virtual para iterar rápido y sin soldador.

¿Lenguajes y herramientas? La base son los HDL: VHDL y Verilog son los estándares, pero también existen ABEL y entornos gráficos como LabVIEW FPGA para subir el nivel de abstracción y revisar herramientas de CAD para diseño electrónico. En el ecosistema libre, destacan Yosys (síntesis), Arachne-pnr y IceStorm (place & route y bitstream para Lattice), Icarus Verilog (simulación) y GTKWave (visualización). Además, IceStudio ofrece un enfoque visual orientado a makers y alumnos, y hay iniciativas como SBA (Simple Bus Architecture) con librerías VHDL portables para armar SoCs en distintas familias.

En la industria, los fabricantes han empujado la síntesis de alto nivel (HLS), acercando el diseño hardware a desarrolladores de software con plataformas como Vivado, Vitis o entornos de Altera/Intel. Esto, combinado con librerías y IPs maduras, ha recortado tiempos de llegada a mercado y ha abierto la puerta a que equipos mixtos software/hardware colaboren con fluidez.

Ventajas e inconvenientes frente a ASIC y CPLD

Históricamente se decía que las FPGAs eran más lentas, consumían más y no servían para sistemas muy complejos. Aunque esas afirmaciones tuvieron base en su día, hoy se sostienen más por inercia que por realidad: las FPGAs contemporáneas son capaces de albergar diseños de enorme complejidad, con frecuencias altas y consumos optimizados, sobre todo en familias orientadas a bajo consumo y edge. Su gran baza sigue siendo la reprogramabilidad y el coste de desarrollo muy inferior al de un ASIC.

Frente a los CPLD, la diferencia se nota en densidad y arquitectura. Un CPLD suele moverse en decenas de miles de puertas lógicas equivalentes y presenta una estructura de “suma de productos” más rígida, mientras una FPGA alcanza cientos de miles o millones y se basa en pequeños bloques interconectables con mayor libertad. Muchas FPGAs incluyen bloques de memoria y DSP embebidos, algo menos habitual en CPLD, que brillan más en glue logic y tareas de control sencillas.

Como contrapartida, el flujo de diseño en FPGA es más exigente: hay que pensar en temporización, restricciones de enrutado y recursos de colocación; pero a cambio obtienes paralelismo masivo y capacidad de iterar y reconfigurar sin tocar una máscara de silicio.

Emulación, prototipado y el “shift-left” en el desarrollo

En muchas empresas de silicio, los primeros prototipos de SoC se mapean en FPGAs para arrancar la integración de software meses antes de tener el chip real. Esta emulación corre órdenes de magnitud más rápido que la simulación, y permite validar interacciones hardware/software con escenarios del mundo real. Aunque la FPGA trabaja a una fracción de la frecuencia final, el tiempo ahorrado en integración y depuración es conmovedoramente grande.

En el terreno educativo y maker, las FPGAs son fantásticas para aprender lógica digital moderna con proyectos prácticos. Puedes recrear desde máquinas arcade, como un Pac‑Man completo con su lógica de juego, hasta radios definidas por software o pipelines de visión por computador. Todo con la ventaja de subir y bajar diseños sin miedo a “romper” nada.

Los centros de datos se han convertido en otro feudo natural de las FPGAs. Microsoft anunció el despliegue de FPGAs en los data centers de Bing tras un piloto con resultados llamativos: +95% de throughput, con solo un +10% de consumo y +30% de coste adicional. Baidu, por su parte, acelera redes neuronales profundas para búsqueda, voz e imagen. En finanzas, bancos como Deutsche Bank o JP Morgan integran FPGAs para análisis de riesgos y negociación de alta frecuencia, recortando latencias de forma drástica y medible.

La industria no se quedó mirando: Altera se sumó a OpenPOWER para combinar CPUs POWER con aceleradores en FPGA, buscando cómputo de altas prestaciones con bajo consumo. En el ámbito nacional, centros como Gradiant llegan con ventaja por su experiencia en nube y en prototipado de comunicaciones sobre FPGA, posicionándose para los retos que vienen.

En sectores críticos como aeroespacial y defensa, las FPGAs llevan años demostrando su valía. Por ejemplo, es habitual usar redundancia modular triple (votación “dos de tres”) para mitigar fallos por radiación. Su capacidad de actualización remota y adaptación a nuevos requisitos operacionales las ha consolidado en ámbitos donde el hardware está expuesto y el margen de error es mínimo.

Ecosistema, comunidad y herramientas abiertas

El movimiento de FPGA abierto ha crecido gracias a figuras muy activas. Tim “Mithro” Ansell ha sido un motor de iniciativas comunitarias; Clifford “oe1cxw” Wolf impulsó IceStorm y SymbiFlow; Juan “Obijuan_cube” González lanzó una serie de tutoriales con enfoque visual en IceStudio; David “fpga_dave” Shah documentó a fondo la Lattice ECP5 para la toolchain SymbiFlow; y Piotr “esden” Esden-Tempski financió con éxito la placa IceBreaker. Nombres como Luke Valenty también son referencia para quienes empiezan y desean caminos de entrada asequibles.

En herramientas, además de las ya citadas, el catálogo profesional incluye Altium Designer (diseño electrónico con soporte para múltiples familias), Quartus (Altera/Intel), ISE y Vivado (Xilinx), ispLEVER (Lattice), ModelSim (simulación HDL/Verilog), Synplify (síntesis), LogicSim (simulación), y plataformas de alto nivel como Vitis. Entre los recursos comunitarios, OpenCores alberga IPs libres; hay foros y portales como FPGA Central; y utilidades como SBA System Creator aceleran la generación de SoCs basados en la arquitectura SBA.

También existen repositorios, FAQs, tutoriales y documentación universitaria (por ejemplo, sobre “Arquitecturas de FPGAs avanzadas”) que cubren desde fundamentos (CPLD, GAL, PLA, PAL, PLD) hasta VLSI, gate arrays o flujos de diseño con LabVIEW. Incluso hay charlas emblemáticas, como la del profesor Bob Brodersen sobre supercomputación de propósito general con reconfiguración, que ayudan a entender por qué esta tecnología escala tan bien en rendimiento por vatio.

Fabricantes, familias y tendencias del mercado

El ecosistema comercial lo lideran Xilinx (ahora parte de AMD) e Intel (tras adquirir Altera en 2015). Lattice Semiconductor empuja fuerte en bajo consumo y tecnología no volátil (flash) con nodos como 90 nm y 130 nm, y desde 2014 ofrece dispositivos RAM combinados con memoria no volátil no reprogramable. Microsemi (antes Actel) apuesta por flash reprogramable; QuickLogic mantiene líneas basadas en antifusibles de única programación; Atmel exploró combos con MCU AVR + FPGA; Achronix se centra en FPGAs muy rápidas; MathStar experimentó con FPOA; y Tabula propuso lógica multiplexada en el tiempo.

El recorrido de Xilinx ilustra bien la evolución del producto: XC2064 como primera FPGA comercial; familias XC4000 y Virtex incorporando RAM y DSP para infraestructura inalámbrica; la línea Spartan (desde 1999) abriendo alternativas de coste contenido; 2001 trajo los primeros SerDes integrados; y en 2011, Virtex‑7 2000T llevó a producción el empaquetado CoWoS (2,5D) hoy fundamental en HPC y en la ola de GPUs para IA. En 2012 llegaron Zynq (SoC adaptativos con Arm) y Vivado Design Suite para facilitar el diseño a perfiles de software.

En 2019, los Versal inauguraron los SoC adaptativos con AI Engines y una red de interconexión en chip (NoC), acompañados por Vitis como plataforma de software unificada con herramientas de IA preoptimizadas. Ya en 2024, la serie Versal AI Edge Gen 2 apostó por integrar lógica programable, CPUs, DSPs y AI Engines para acelerar IA extremo a extremo en un solo chip, y la familia Spartan UltraScale+ amplió el catálogo de soluciones de coste y consumo ajustado para aplicaciones con E/S intensivas en el borde. Todo ello refleja una tendencia clara: combinar heterogeneidad y eficiencia en un solo silicio reconfigurable.

Aplicaciones frecuentes y dominios de uso

Las FPGAs aparecen en DSP, radio definida por software, sistemas aeroespaciales y de defensa, prototipado de ASIC, imagen médica, visión por computador, reconocimiento de voz, bioinformática y emulación de hardware. También brillan en aceleración de IA (inferencia optimizada), redes (offload de paquetes, inspección profunda), cifrado y compresión, y en el mundo industrial (control, sensórica, tiempo real). Cuando necesitas paralelismo masivo, latencia baja y capacidad de adaptar el hardware a la carga, una FPGA suele ser buena candidata.

Para quienes parten de cero, hay comunidades y grupos de trabajo en español, foros especializados, wikis y bases de datos de dispositivos, además de colecciones de “cores libres” con licencias abiertas (incluida GPL) que abarcan desde microprocesadores y filtros hasta módulos de comunicaciones y memorias. Esta disponibilidad acelera prototipado, reduce costes y fomenta el aprendizaje práctico.

Conceptos relacionados y terminología útil

Al explorar este mundo es común cruzarse con términos como gate array, VLSI, ASIC, CPLD, GAL, PLA, PAL, PLD, circuitos integrados y hardware en general. También aparecen referencias a metodologías con LabVIEW, a GSD o a documentación sobre “cómo funciona la lógica programable”. Todos ellos forman parte del vocabulario que conviene tener en la mochila cuando se trabaja con reconfigurable.

Por supuesto, el estándar de descripción es clave: VHDL y Verilog dominan el panorama, con flujos que incluyen simulación (ModelSim, Icarus Verilog), síntesis (Synplify, Yosys), place & route (herramientas de cada fabricante y alternativas libres como Arachne‑pnr), análisis temporal, y visualización con GTKWave. En paralelo, entornos gráficos como LabVIEW FPGA o iniciativas educativas como IceStudio facilitan la curva de entrada.

Mirando hacia atrás, queda claro que las FPGAs han pasado de ser “prototipos programables” a un pilar del cómputo moderno: conviven con CPUs y GPUs, aceleran cargas críticas, permiten actualizar hardware como si fuera software y ofrecen un campo de juego donde makers, estudiantes y profesionales pueden construir desde un Pac‑Man hasta un centro de datos. Con IA, edge y seguridad empujando fuerte, y con familias como Versal, Zynq o Spartan UltraScale+ en plena forma, todo apunta a que la evolución seguirá muy viva en los próximos años.