La idea de que cualquiera pueda encargar silicio personalizado sin arruinarse ya no suena a ciencia ficción: wafer.space plantea una vía para fabricar tus propios chips a un coste de 7 dólares por die aprovechando corridas conjuntas en una tecnología madura y documentada. El planteamiento recuerda a lo que en su día supuso abaratar las placas PCB, pero llevado al terreno del circuito integrado.

En este análisis te contamos con detalle cómo funciona la iniciativa, qué ofrece la primera corrida en la plataforma GF180MCU, qué necesitas para subir tu diseño y qué papel puede jugar RISC-V si quieres integrar un procesador abierto en tu chip. También ponemos en contexto este movimiento frente a la carrera por la fabricación de semiconductores para IA, con proyectos multimillonarios como los que se asocian a OpenAI, TSMC y los grandes fondos internacionales.

Qué propone wafer.space y por qué se habla de 7 dólares por die

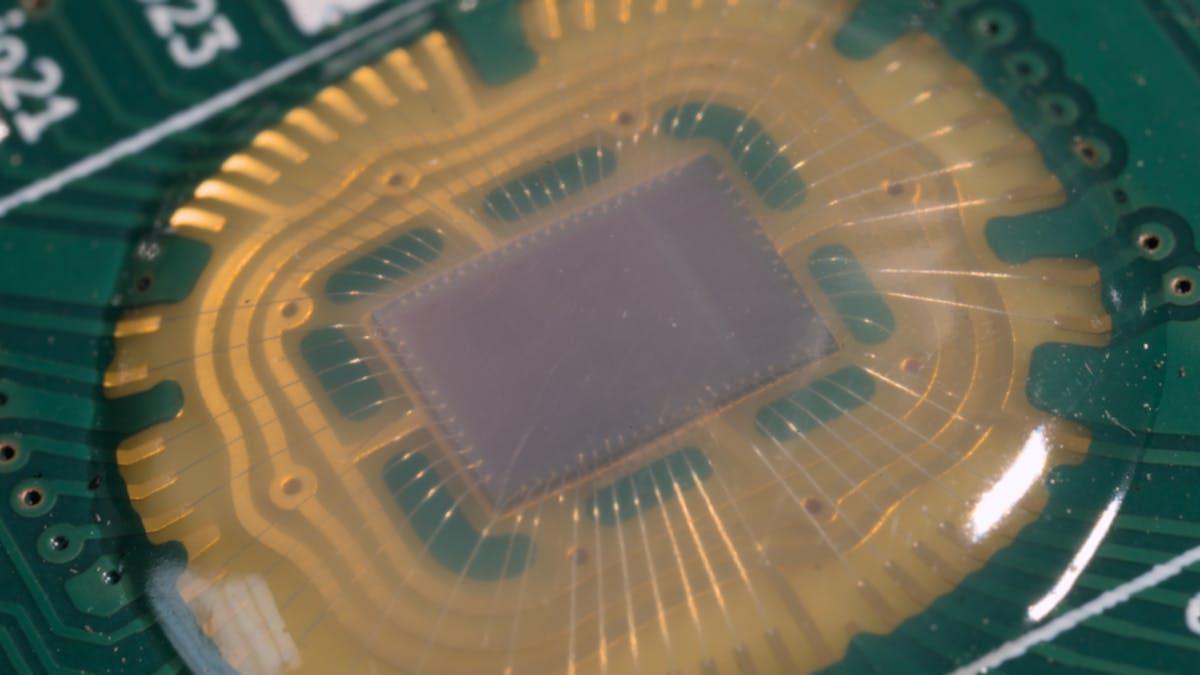

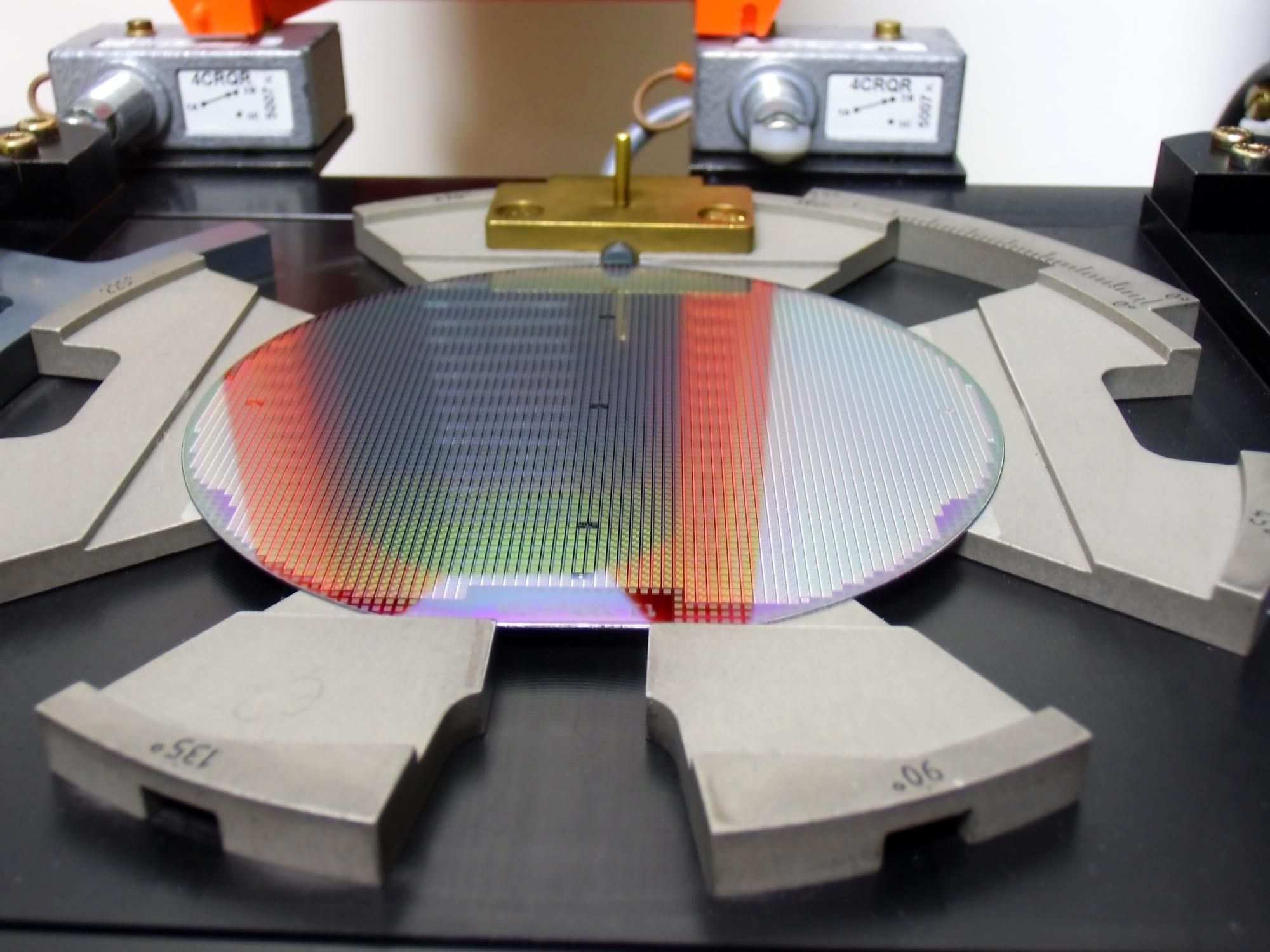

wafer.space ha abierto su primera corrida de fabricación conjunta en la tecnología GF180MCU, con una fecha límite de compra fijada para el 28 de noviembre de 2025. La descripción oficial lo compara con un “OSH Park para silicio”: compartes oblea con otros, optimizas costes y recibes tus dies fabricados a un precio muy por debajo de una tirada privada tradicional.

El gancho de “7 dólares por die” sintetiza la ambición: acercar el silicio a desarrolladores, laboratorios y pequeñas empresas que antes solo podían prototipar en FPGA. La clave está en el modelo de shuttle o corrida conjunta, donde múltiples diseños se panelizan en una misma oblea para repartir gastos de máscara y proceso.

La oferta se articula a través de una página de campaña en Crowd Supply para “GF180MCU Run 1”, donde se efectúa la reserva de plaza y la compra. Puedes consultarla en https://www.crowdsupply.com/wafer-space/gf180mcu-run-1/, el punto de entrada para conocer cupos, especificaciones y el calendario.

Para los curiosos, GF180MCU es un proceso de 180 nm con materiales y bibliotecas documentadas públicamente; su PDK abierto está disponible en https://gf180mcu-pdk.readthedocs.io/. La disponibilidad de documentación y celdas estandarizadas hace viable un flujo de diseño basado en herramientas de código abierto, reduciendo aún más la barrera de entrada para equipos pequeños.

Cómo funciona la corrida conjunta GF180MCU

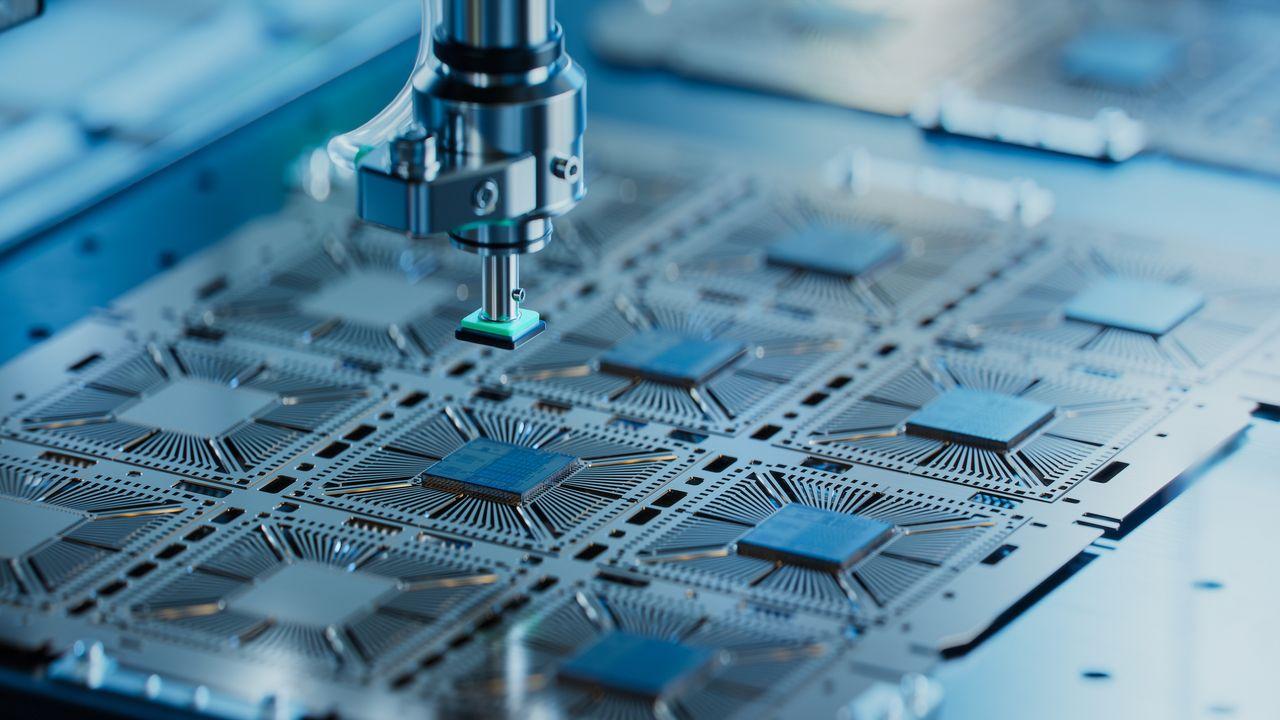

El mecanismo es simple: aportas un diseño de hasta 20 mm2 para la tecnología GF180MCU y, una vez fabricada la oblea, recibes 1.000 piezas correspondientes a tu bloque. Esta cuota de superficie, 20 mm2, marca el presupuesto de área para lógica, memoria, pads y cualquier IP que integres; es un límite generoso para controladores, ASICs específicos o microcontroladores personalizados con aceleradores.

Un detalle interesante es que no tienes por qué partir de cero. Se puede emplear una plantilla ya existente o construir el chip completamente desde cero, en función de tu experiencia, plazos y ambición. Eso acelera el time-to-silicon para quienes quieren iterar rápido sin arriesgar la primera vez.

En cuanto a herramientas, la iniciativa no te encierra en un único ecosistema: se admite el uso de suites de código abierto como LibreLane, Magic o KLayout, así como flujos propietarios si ya formas parte de un entorno empresarial. La flexibilidad de herramientas evita fricciones y permite adaptar el flujo a las capacidades de cada equipo, tanto si prefieres scripts y herramientas comunitarias como si dispones de licencias EDA comerciales.

Otro punto a favor es que no se exige anillo de pads (“pad ring”) ni una CPU de gestión dedicada para la entrega. Esto simplifica el empaquetado lógico del diseño y evita ataduras a plataformas específicas, algo muy útil cuando el objetivo es incorporar el mínimo imprescindible para validar la idea en silicio.

El calendario es claro: la fecha límite de compra es el 28 de noviembre de 2025, una ventana suficientemente amplia para preparar la netlist, verificación y cierre físico. Ese hito marca el cierre de inclusión en la oblea compartida; a partir de ahí, la fabricación y el test siguen el cronograma de la foundry.

Herramientas de diseño: de KLayout y Magic a flujos abiertos

El PDK de GF180MCU, accesible en la documentación pública de la foundry, facilita un abanico de opciones para el diseño. Herramientas como Magic y KLayout son referentes para layout y revisión visual, con comunidades muy activas y abundantes ejemplos de uso en procesos maduros.

Para automatización de síntesis y place & route, la referencia a LibreLane apunta a un flujo de herramientas abiertas integradas, con scripts para llevar desde RTL a GDS. Este enfoque es atractivo si quieres reproducibilidad y pipelines CI: el mismo script que corre en tu portátil puede ejecutarse en un servidor y generar el mismo resultado.

Si ya trabajas con EDA comercial, no estás limitado: puedes usar tu flujo propietario para verificación formal, temporización y cierre físico, exportando GDS final compatible con GF180MCU. La compatibilidad del PDK con herramientas del mercado asegura que las empresas no tengan que reentrenar equipos ni rehacer librerías desde cero.

Un consejo práctico para equipos pequeños: empieza por una plantilla o SoC minimalista verificado, añade tu IP y valida con testbenches agresivos. Los costes del shuttle son competitivos, pero cada spin de silicio sigue requerindo disciplina de verificación; invertir tiempo en test te ahorrará disgustos tras el tape-out.

RISC-V como arquitectura lista para integrar

Si tu chip necesita un procesador embebido, RISC-V es el candidato natural. Se trata de una arquitectura de conjunto de instrucciones modular, extensible y libre de licencias, nacida en Berkeley y hoy adoptada en un abanico enorme de productos. Hay ejemplos que van desde microcontroladores CH32V003 de 0,10 dólares hasta iniciativas paneuropeas de supercomputación, pasando por estaciones de trabajo de 64 núcleos a 2 GHz en el terreno profesional.

RISC-V encaja muy bien en dos escenarios útiles para este tipo de corridas: como núcleo blando en un FPGA para prototipado rápido, y como CPU integrada en tu SoC a 180 nm para control y tareas generales. Incluso como máquina virtual de alto rendimiento en software, RISC-V ha demostrado versatilidad, lo que te permite validar tu stack de software antes de tener el silicio real.

Además, su ecosistema abierto facilita reutilizar toolchains, depuradores y RTOS sin dependencia de licencias. Para más información y recursos, la web oficial es https://riscv.org, un buen punto de partida para elegir un core, extensiones y soporte de software.

Fechas, cantidades, área y requisitos: lo esencial

Resumiendo la oferta: tienes hasta el 28 de noviembre de 2025 para efectuar la compra y asegurar tu slot en la oblea compartida GF180MCU. El diseño puede ocupar hasta 20 mm2 y, tras la fabricación, recibirás 1.000 unidades, una cantidad idónea para validación, kits de desarrollo internos o primeras demos para clientes.

La metodología no te impone un anillo de pads fijo ni controlador de gestión, lo que te da libertad para priorizar tu lógica o IP. Puedes arrancar con una plantilla existente para minimizar riesgos o construir todo a medida si tu equipo ya tiene experiencia en cierres físicos y verificación.

En el flujo, combinan bien herramientas abiertas como LibreLane, Magic y KLayout con utilidades propietarias, siempre y cuando el resultado sea un GDS y verificación acordes con el PDK de 180 nm. La documentación pública del PDK de GF180MCU en https://gf180mcu-pdk.readthedocs.io/ es clave para despejar dudas sobre reglas de diseño, capas, bibliotecas y parámetros eléctricos.

Y sí, el mensaje que corre por la comunidad—“7 dólares por die”—se entiende mejor en el contexto de una corrida conjunta: se trata de democratizar el acceso al silicio asumiendo que compartes oblea y costes con otros diseños, un modelo probado que traslada al chip la filosofía colaborativa que ya triunfó en la fabricación de PCB.

El contexto industrial: de un “OSH Park para silicio” a la fiebre por los chips de IA

Mientras iniciativas como la de wafer.space empujan el acceso a silicio de forma horizontal, en el otro extremo del espectro se están moviendo montañas de capital para asegurar capacidad de fabricación de nueva generación, centrada en IA. Según varias informaciones, el CEO de OpenAI, Sam Altman, ha iniciado una recaudación de fondos para levantar una red de fundición y asegurar chips personalizados para sus modelos.

En una de las vertientes divulgadas, los principales interesados serían G42 (conglomerado de IA de Abu Dhabi) y SoftBank Group (propietaria de ARM), con una inversión apuntada entre 8.000 y 10.000 millones de dólares para desplegar capacidad a medida. En paralelo, se ha informado de conversaciones para levantar entre cinco y siete billones de dólares destinados a ampliar drásticamente la infraestructura global de semiconductores enfocada a IA.

Esas cifras mareantes contrastan con el espíritu de un shuttle accesible, pero dibujan el mismo telón de fondo: la demanda de cómputo para IA está limitada por la escasez de GPU, esenciales para entrenar y ejecutar grandes modelos por su capacidad para multiplicaciones de matrices en paralelo.

En este escenario, TSMC—la mayor foundry independiente del mundo—es un pivote industrial del que dependen compañías como Nvidia, Apple, Intel o AMD para producir SoC, CPU y GPU. La participación de TSMC y de inversores internacionales como los EAU subraya el carácter estratégico de la fabricación, con implicaciones geopolíticas y regulatorias evidentes.

Estados Unidos, consciente del peso de los semiconductores en la economía digital y la seguridad nacional, ha intensificado el apoyo doméstico: la administración Biden ha anunciado 5.000 millones de dólares para I+D en tecnologías de semiconductores y ha reforzado el escrutinio sobre inversiones extranjeras en sectores críticos. En paralelo, TSMC invierte 40.000 millones de dólares en su planta de Arizona, una de las mayores apuestas de capital extranjero en la historia del país.

Para quienes van a aprovechar GF180MCU, esta macro‑tendencia importa porque estabiliza cadenas de suministro, acorta plazos y promueve la estandarización de PDKs abiertos. Que exista un carril “low cost” para prototipar no compite con el “high end” de 5 nm y 3 nm, pero ambos mundos se retroalimentan y fortalecen el ecosistema.

Consejos prácticos para llegar a tiempo al tape-out

Organiza el proyecto en dos carriles: especificación y verificación por un lado, y cierre físico por otro. Congela el conjunto de instrucciones (si usas RISC-V) y define interfaces desde el principio, para evitar cambios de última hora que compliquen placement y rutas.

Reutiliza IP probada donde tenga sentido: UART, SPI, I2C, temporizadores y GPIO suelen estar disponibles en repositorios abiertos. Dedica tus recursos al diferenciador (acelerador, filtro, DSP, cifrado, etc.), y no reinvents la rueda en periféricos básicos.

Automatiza con scripts todo lo que puedas: síntesis, P&R, DRC, LVS y generación de GDS. Un pipeline reproducible reduce errores humanos y acelera iteraciones cuando aparecen violaciones de reglas o problemas de temporización.

En validación post-silicio, planifica desde ya el bring-up: qué encapsulado usarás, cómo se alimenta, qué pines de test necesitas y qué firmware mínimo cargará la primera vez. Cuanto más claro esté el plan de laboratorio, menos tiempo perderás cuando lleguen tus 1.000 piezas.

El movimiento que representa wafer.space acerca el silicio a equipos de todos los tamaños, y lo hace con reglas claras: un área de 20 mm2, 1.000 unidades y una fecha límite de 28 de noviembre de 2025. Con un PDK abierto como GF180MCU y herramientas accesibles (LibreLane, Magic, KLayout o flujos propietarios), se abre la puerta a que muchos diseños que hoy viven en FPGA salten al mundo del ASIC. Mientras tanto, en la otra punta del espectro, los megaproyectos de IA y la inversión geopolítica en semiconductores empujan la industria hacia más capacidad y mejores procesos. Entre ambos extremos, se está construyendo un puente que permite innovar desde abajo sin perder de vista la ola que viene por arriba.