Europa tiene una fuerte dependencia de la tecnología diseñada y producida en Estados Unidos y China. Por eso, desde hace unos años, se están moviendo algunas cosas a nivel de la UE para que esto deje de ser así, y poder tener independencia, especialmente en la computación. De estos movimientos han surgido proyectos como EPI, eProcessor, empresas como SiPearl, así como la infraestructura GAIA-X.

Dado que la mayoría de las ISAs o arquitecturas son propietarias y están en manos fuera de Europa, el código abierto ha sido clave para que estos proyectos puedan salir adelante. La ISA RISC-V ha traído la esperanza, permitiendo que estos procesadores y aceleradores se basen en ella sin ningún tipo de restricción ni limitación por guerras geopolíticas y geoestratégicas.

Nace EPI (European Processor Initiative)

Una de las primeras reacciones de Europa, tras la conferencia de EDA (European Defense Agency) donde se expusieron los problemas por la dependencia tecnológica e industrial de los países miembros, fue iniciar una iniciativa conjunta denominada EPI (European Processor Initiative). Su objetivo es agrupar un consorcio para poner en marcha los mecanismos necesarios para disponer de procesadores diseñados en Europa.

Estos chips, en principio, no serán para uso particular, sino que se centrarán en el sector HPC, es decir, la supercomputación. Estas máquinas de alto rendimiento son especialmente críticas, y con el fruto de este proyecto se impulsará a los centros de datos de la UE hacia la Exaescala a partir de 2023. También tendrán aplicación en otros sectores como la industria del automóvil y la aeroespacial.

Para hacer esto posible, se han basado en RISC-V para los aceleradores, mientras que los GPP o procesador de propósito general, se basarán en núcleos IP ARM Cortex Neoverse, dado que les permitirán acelerar el proceso de diseño y no comenzar desde cero.

EPI cuenta también con 26 socios de 10 países europeos distintos, entre ellos España. Uno de los pilares centrales del proyecto es el Centro Nacional de Supercomputación de Barcelona (BCN). A España se unen socios como Chalmers Tekniska Hoegskola AB de Suecia, Infineon Technologies de Alemania, CEA de Francia, STMicroelectronics en Holanda, la Università di Bologna de Italia, el Instituto Superior Técnico de Lisboa en Portugal, FORTH de Grecia, o el laboratorio ETH Zürich de Suiza.

Se crea SiPearl, la empresa privada para dotar al proyecto de capacidad de operar

Para poder operar, se ha creado una empresa privada que se encargará de gestionar las tecnologías resultantes de este proyecto EPI. Su nombre es SiPearl y su cuartel general se encuentra en Francia. Además, han abierto una filial en Alemania y otra en España, concretamente en Barcelona, para así estar cerca de sus socios del BSC.

Esta startup partía con un presupuesto público de 80 millones de euros, que no son suficientes para cubrir todos los gastos que un proyecto de tal calado implica. Por tanto, SiPearl también se encargará de recaudar más de 100 millones de euros privados, principalmente de acciones.

Su co-fundador y CEO, Philippe Notton, está haciendo una labor fantástica reclutando a algunos diseñadores traídos desde Silicon Valley, así como el personal adecuado con la experiencia para dotar al proyecto de todas las garantías. También están buscando socios a nivel tecnológico, como es el caso de Graphcore, una compañía británica líder en cuanto a aceleración chips con inteligencia artificial que resultan tan importantes en el HPC.

BSC un socio clave: Del chip Lagarto hasta Drac

El BSC (Barcelona Supercomputing Center) es una pieza clave de este proyecto. No solo están contribuyendo al diseño y desarrollo de estos procesadores, sino que el Marenostrum 5 comenzará ya a probar los frutos de este proyecto…

Lagarto

El primer microprocesador español basado en el repertorio de instrucciones RISC-V se ha bautizado como Lagarto, y es el primer paso para llegar a la independencia tecnológica. Sin embargo, tras este proyecto hay un gran esfuerzo y trabajo coordinado por el BSC del Centro Nacional de Supercomputación de España, así como la colaboración del CSIC, y la UPC.

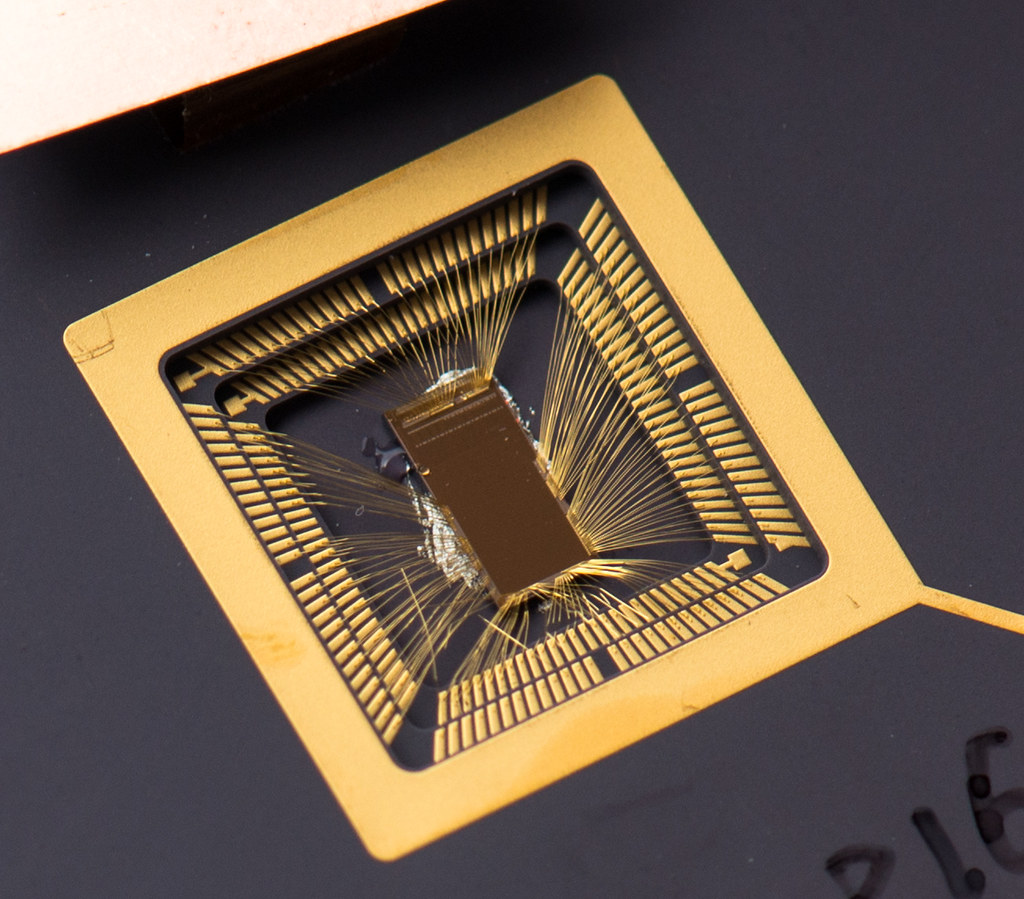

Este diseño es muy sencillo, y su objetivo es realizar las primeras pruebas. Se fabricó usando un nodo de 65nm en TSMC, suficiente para la relativa sencillez de este prototipo temprano que fue probado en algunos benchmarks para ver de qué era capaz, y los resultados fueron bastante positivos. Incluso mejor de lo esperado…

En mayo de 2019 se enviaría el diseño final de este chip a la plataforma EUROPRACTICE de la CE, y tras eso llegarían unos 100 ejemplares de Lagarto a Barcelona para comenzar con las pruebas y que sirva como base para el acelerador para el HPC que se está basando también en esta ISA.

DRAC

El siguiente paso fue DRAC (Designing RISC-V-bsed Accelerators for the next generation Computers). Un chip diseñado para aplicaciones de seguridad, como el cifrado por hardware, así como también aplicaciones científicas como el análisis del genoma, aceleración de simulaciones, o el sector de los vehículos autónomos.

Por supuesto, DRAC también está liderado por el BSC y se basa en la arquitectura de código abierto RISC-V. Este proyecto tiene previsto durar unos 3 años, en la que participarán hasta 40 investigadores y será coordinado por Miquel Moretó, un investigador del programa Ramón y Cajal de la UPC. Además, la financiación ha sido de unos 4 millones de euros, la mitad procedentes de fondos FEDER y la otra mitad de los socios de este proyecto.

Esto ya ha comenzado a dar sus frutos. DVINO (DRAC Vector IN-Order) es un chip derivado de este proyecto y de primera generación. Como su propio nombre deja intuir, se trata de un CI en orden que incluye un núcleo Lagarto junto con un procesador vectorial Hydra pensado para la computación distribuida.

La segunda generación mejorar el rendimiento del chip en un 15% y añade nuevos controladores y se ha incrementado el área hasta 8.6 milímetros cuadrados.

eProcessor

eProcessor es el nuevo paso al frente, un procesador con versiones previstas para la supercomputación y servidores, así como sistemas avanzados de asistencia al conductor para vehículos (p.e.: ADAS), IoT, dispositivos móviles, etc.

Nuevamente el BSC es el que está inmiscuido en este proyecto. Se trata del primer ecosistema full-stack europeo de código abierto y cuyo pilar central será una CPU basada en RISC-V y con un núcleo con ejecución fuera de orden. El centro de Barcelona aportará su experiencia en el diseño de núcleos IP en HDL, emulación, y herramientas necesarias.

Junto con el BSC, se han implicado otros miembros importantes a nivel europeo, como la Universidad Tecnológica de Chalmers, la Foundation for Research and Technology Hellas, Universita degli Studi di Roma La Sapienza, Cortus, Christmann Informationstechnik, Universität Bielefeld, Extoll GmbH, Thales y Exapsys, así como el respaldo de EuroHPC JU.

Se desarrollarán tecnologías de hardware y software que se comenzarán probando en FPGAs para luego dar el salato a los ASICs. El primer paso será diseñar un núcleo RISC-V de alto rendimiento y alta eficiencia. Será un single-core y un dual-core con enlace coherente off-chip, aunque luego se comenzarán con diseños más complejos y potentes. También se diseñará el acelerador vectorial basado en RISC-V y se explorarán cargas de trabajo tradicionales en supercomputación, como la bioinformática, IA, HPDA, etc.

El eProcessor será también muy versátil y flexible a la hora de escalarlo, para poder ir agregando más dispositivos on-chip.

El siguiente paso: la fabricación

El diseño de estos chips será europeo, lo que no será es la fabricación. SiPearl es una fabless, y dado el atraso en cuanto a los nodos de fabricación de las foundries en países miembros, el diseño se ha encargado a TSMC, que lo fabricará en tecnología de 7nm y usando la novedosa tecnología de empaquetado 3D denominada CoWoS (Chip-on-Wafer-on-Substrate).

Sin embargo, la idea es no depender de factorías extranjeras para eso, por lo que la UE también ha movilizado una gran parte de dinero para financiar la puesta al día de la fabricación de semiconductores en el Viejo Continente. Concretamente destinará 145.000 millones de euros, con el objetivo de llegar a un nodo con tecnología de fabricación de 2nm a corto plazo.

Esto necesita de tiempo, y se pretende que llegue a 2-3 años vista. Además, parece que TSMC está colaborando en que esto sea posible, y también la europea ASML, que es el líder en cuanto a la fabricación de máquinas para la fotolitografía avanzada para la industria de los semiconductores, y que tiene sede en Países Bajos…

La propia Nadia Calviño, vicepresidenta de Asuntos Económicos y Transformación Digital lo ha explicado así: «Se está trabajando a nivel nacional e internacional para ver qué empresas españolas y europeas pueden fabricarlos«, en referencia e estos chips. En la misma línea fue el discurso de Thierry Breton en la Comisión Europea. Y es que los fondos destinados al sector saldrán en gran medida de las ayudas prestadas por la UE para la transformación digital y para la recuperación post-pandemia.